Zilog EZ80F91 User Manual

Page 48

eZ80F91 Development Kit

User Manual

UM014220-0508

eZ80F91 Module

43

eZ80F91 device (a generic feature of the eZ80

®

family when it is used in

native mode). The discussion that follows references

.

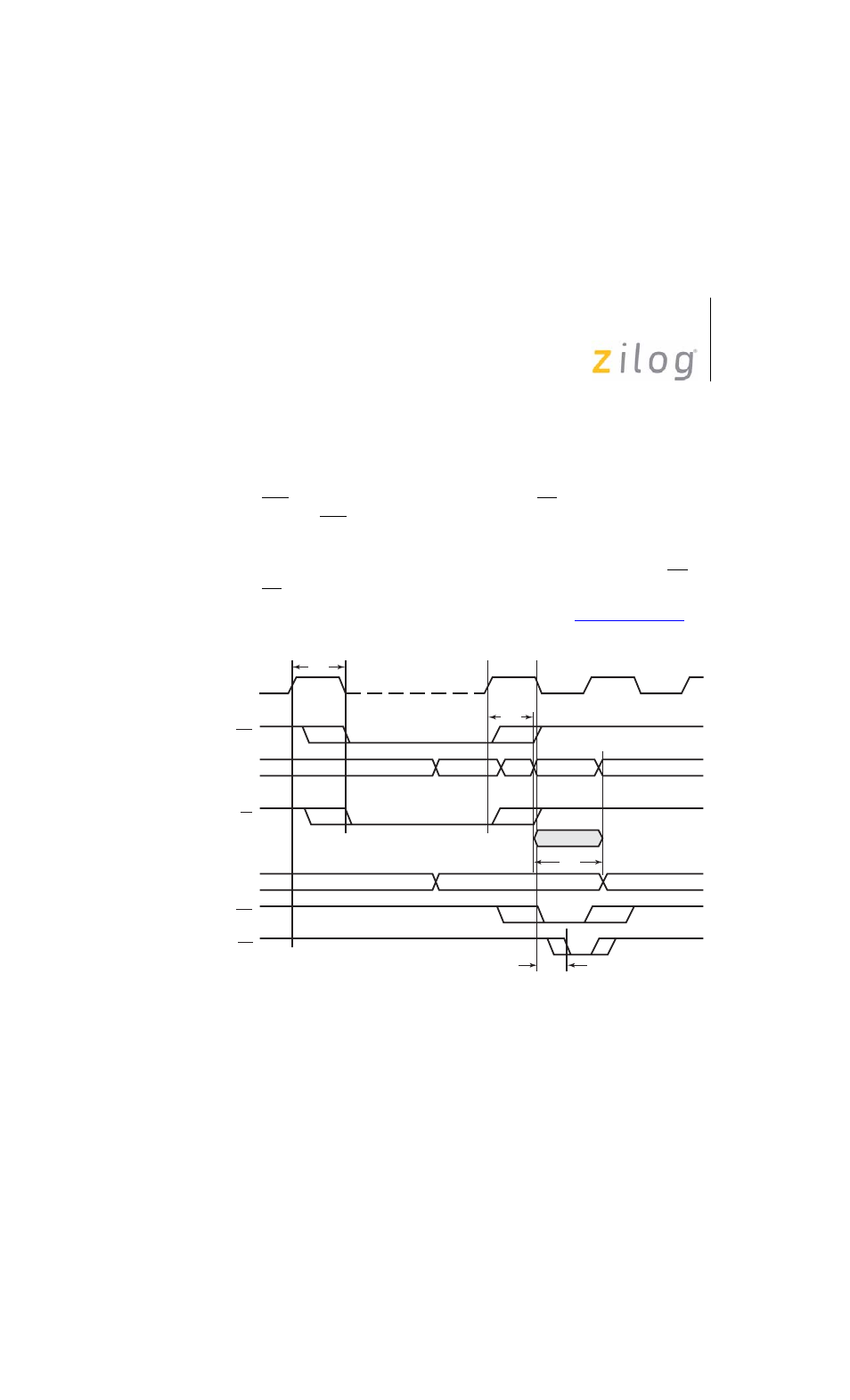

Bus contention can occur when two or more devices drive a common bus.

CS0 on the eZ80F91 device drives the Flash CE. Upon accessing Flash

memory, CS0 is driven High a maximum of 8.8 ns after the next rising

edge of the CPU Clock (T6—refer to the External Memory Read Timing

diagram in the eZ80F91 MCU Product Specification (PS0192) for assis-

tance). The Flash turn-off time (T

OD

) is 25 ns—the duration from OE or

CE going High to Flash output drivers in a high-impedance state. For fur-

ther information, refer to MT28F008 data sheet

Figure 11. Possible Bus Contention without Fast Buffer

T6

T3

T4

T

Data In

Data Out

OD

Bus Contention

CPU Clock

CS0

CS1

eZ80F91 Data Bus

Flash Data Bus

RD

WR