Jumper settings, Zilog developer studio, Ez80ac – Zilog EZ80F91AZA User Manual

Page 26: Sted in, Table 2

Appendix A

UM024402-0812

16

eZ80AcclaimPlus! Development Kit

User Manual

If the Board is powered via a wall outlet and P3 is not used, communication with the PC

can be established through a DB9 female connector (P4) which is connected to the

UART1 block of the eZ80F91 MCU.

All signals that control access to on-board memory are routed to the Board’s test points;

please refer to

Appendix B. Schematic Diagrams

Jumper Settings

All available GPIO ports that exist on the eZ80F91 MCU are routed to connector J10,

which is a standard 0.1"-pitch header. These signals are only routed to the odd-numbered

pins; all even-numbered pins are connected to GND. Please refer to

on page 18 for the exact signal connections to J10. The remaining jump-

ers are described in Table 2.

Zilog Developer Studio

The Zilog Developer Studio II Integrated Development Environment (ZDS II IDE) is a

complete stand-alone system that provides a state-of-the-art development environment.

Designed to run on the Windows Vista, Windows 7 and Windows XP Professional operat-

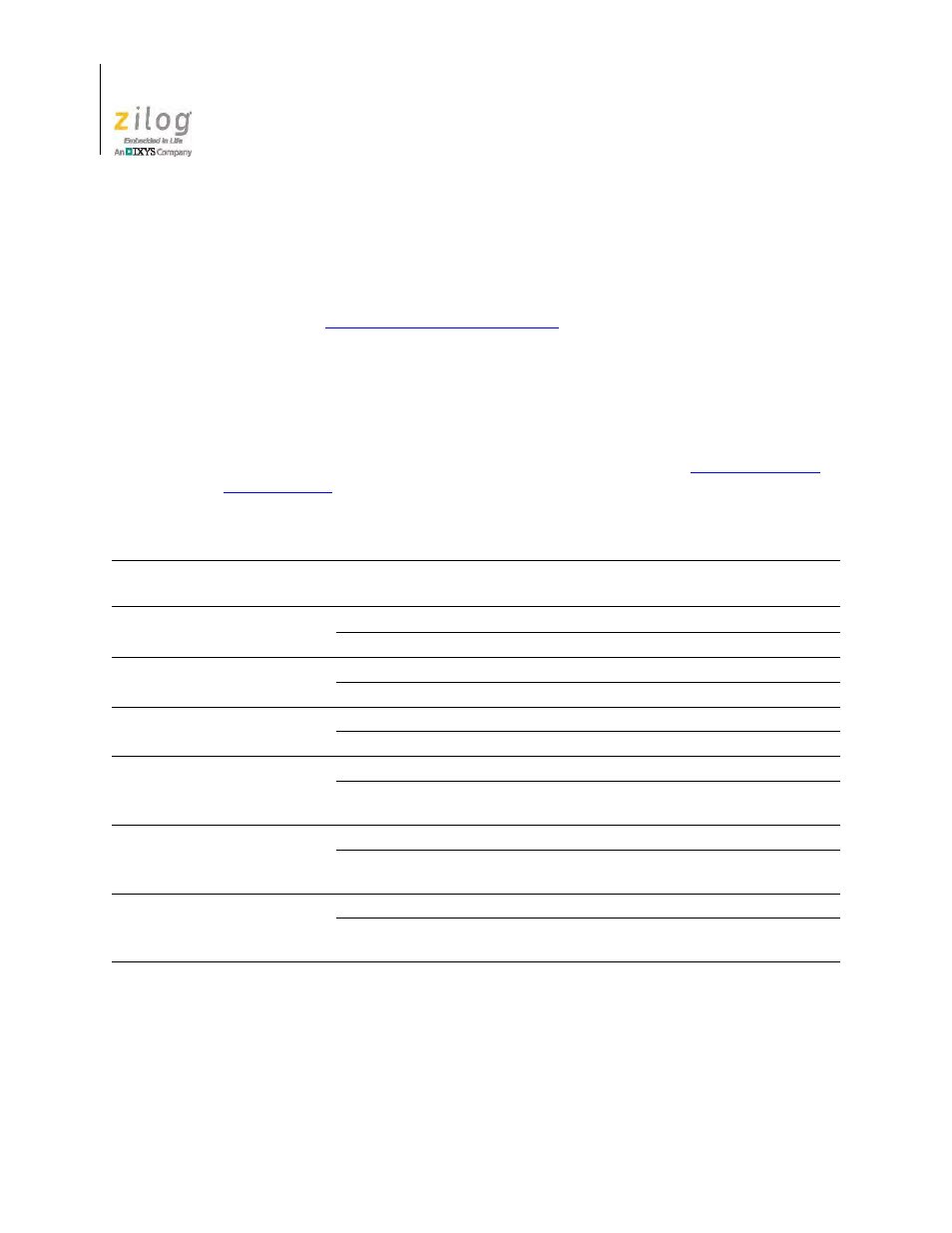

Table 2. eZ80AcclaimPlus! Development Board Jumper Settings

Jumper

Name

Description

State

Function

Factory

Setting

J11

Flash WP

In

On-board Flash is disabled for writing.

Out

On-board Flash is enabled for writing.

Out

J12

Power Source

1–2

USB Powered.

In

2–3

Wall Powered.

J26

RTC_V

CC

In

RTC is powered by on-board V

CC

.

In

Out

External 3.3V source should be connected to J26.2

J25

RXD0

1–2

Pin L12 of U1 (PD1_RXD0) is connected to J10.61

2–3

Pin L12 of U1 (PD1_RXD0) is connected to U8.1

(TXD).

In

J24

RXD1

1–2

Pin G10 of U1 (PC1_RXD1) is connected to J10.45.

In

2–3

Pin G10 of U1 (PC1_RXD1) is connected to U10.12

(R1OUT).

J23

CTS1

1–2

Pin F12 of U1 (PC3_CTS1) is connected to J10.41.

In

2–3

Pin F12 of U1 (PC3_CTS1) is connected to U10.9

(R2OUT).