Ez80acclaim pl – Zilog EZ80F91AZA User Manual

Page 24

Appendix A

UM024402-0812

14

eZ80AcclaimPlus! Development Kit

User Manual

Schematic diagrams for the eZ80AcclaimPlus! Development Board are provided in the

The eZ80AcclaimPlus! Development Board is driven by the eZ80F91 MCU with an exter-

nal 50 MHz (Y1) crystal and an on-chip PLL programmed to run on the eZ80F91 MCU at

its internal frequency of 50 MHz. The chip employs an Ethernet Media Access Controller

(EMAC) with a Media-Independent Interface (MII) that allows the eZ80F91 MCU to it to

interface to all available industry-standard PHYs.

For this eZ80AcclaimPlus! implementation, the ICS1894-40 (U5) was selected to provide

a suitable price/performance solution.

Debug connector (J1) provides access to the eZ80F91 MCU so that the user can download

and control the execution of the sample projects provided with the Kit or his/her own proj-

ect(s) using the USB Smart Cable included in the Kit.

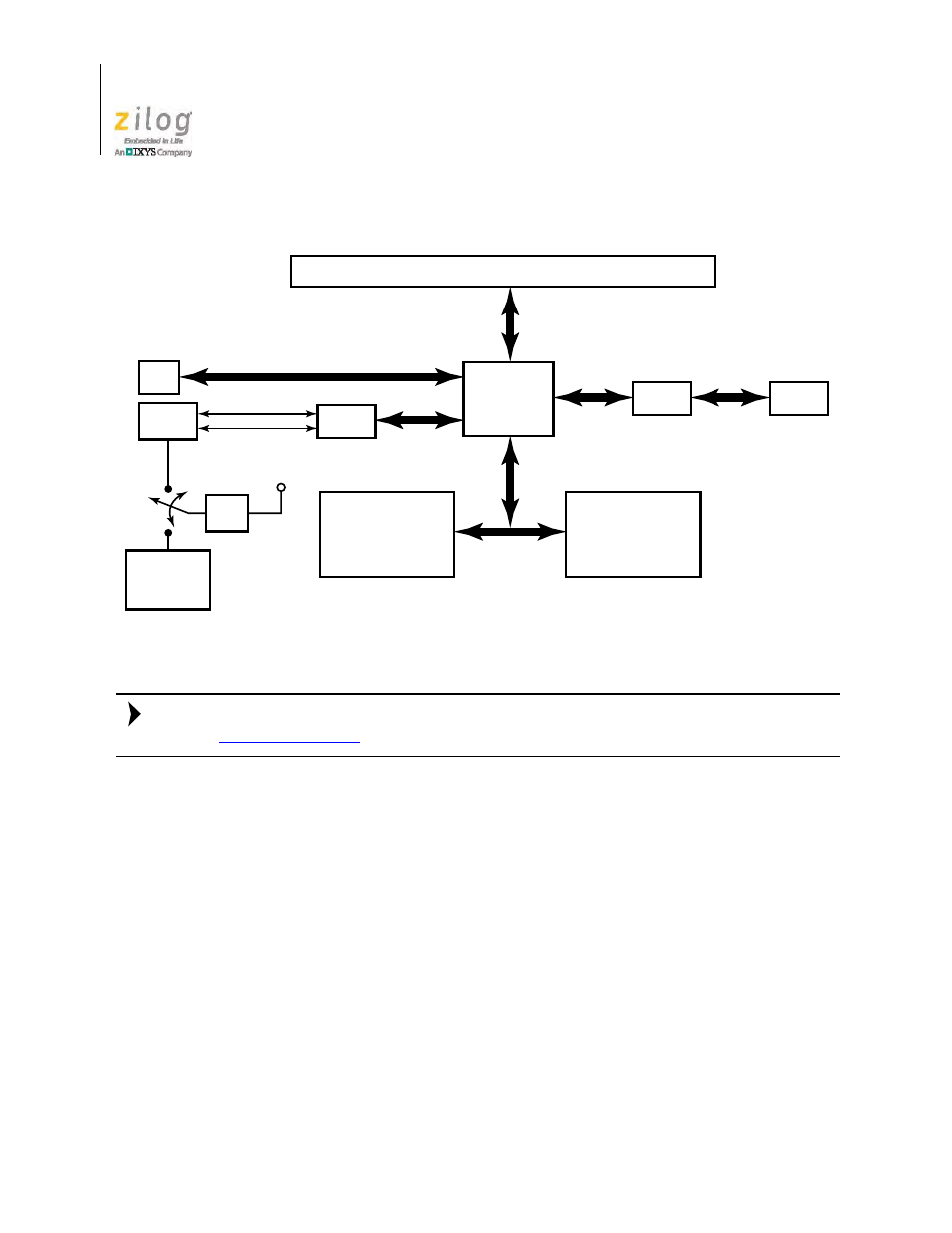

Figure 7. eZ80AcclaimPlus! Development Kit Block Diagram

GPIO Connector

eZ80F91

144BGA

5MHz/PLL

PHY

FTDI

USB

Mini-B

External

Power

Up to 1.5A

SRAM

(1MB, 2 x 512KB)

Flash

(8 MB)

LDO

DB9

RJ45

MAGN

ICS1894

J3011

S29GL064N

CY7C1049DV33-10ZSXI x 2

3.3V/

400mA

UART0

MII

UART1

Note: