Synthesizing fifo partitioner functions, Native synthesis using the quartus ii software – Altera First-In-First-Out Partitioner User Manual

Page 20

18

Altera Corporation

FIFO Partitioner Megafunction User Guide

Getting Started

Synthesizing FIFO Partitioner Functions

The HDL output file generated by the FIFO Partitioner MegaWizard can

be synthesized using standard techniques. The HDL output file

instantiates an instance of alt_csm_core. alt_csm_core.vhd and the

other HDL files it depends on are located in the

<quartus directory>\libraries\megafunctions directory.

Native Synthesis Using the Quartus II Software

Because the necessary files are located in the MegaFunctions directory, the

files are automatically detected by the Quartus II software during

synthesis. No special steps are required to synthesize the FIFO Partitioner

function in the Quartus II software.

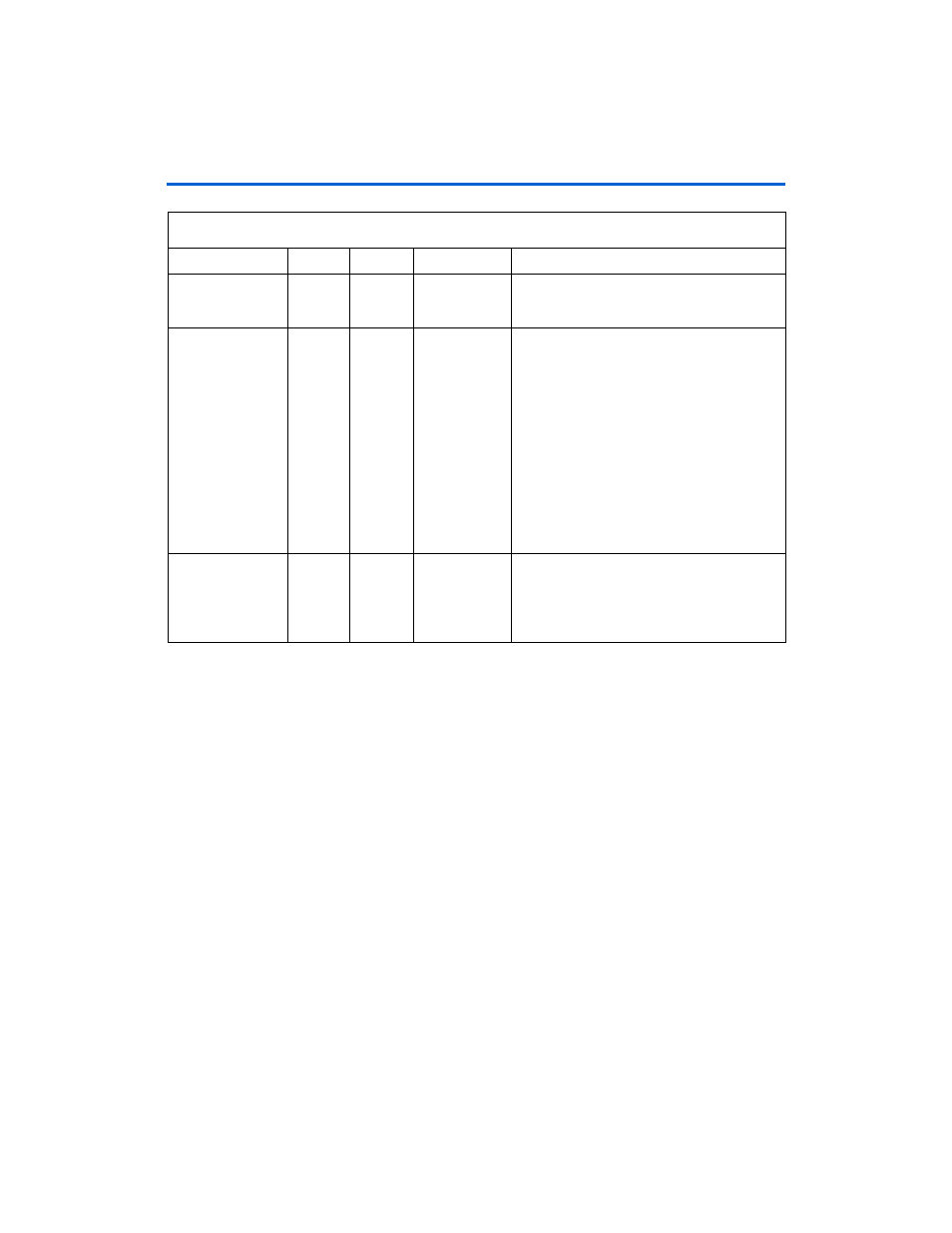

rd_full_n

Yes

Out

Port b full flag

for FIFO n

The read side FIFO full bus. This flag is

synchronous to the read port clocks. This flag has

one cycle of latency.

rd_empty_n

Yes

Out

Port b empty

flag for FIFO n

The read side FIFO empty flag. This flag is

synchronous to the individual read port clocks.

This port may assert for one or two read port

clock cycles at times when the FIFO is not empty

but the zero-latency output buffer does not have

data available. The user is restricted from reading

from a FIFO whenever its

rd_empty_n

flag is

asserted.

When a FIFO is configured with

read_b_n

as a

read acknowledge,

rd_empty_n

also acts as

an active-low data valid flag, that is, data on

rd_data_n

is not valid while

rd_empty_n

is

asserted in read acknowledge mode.

rd_level_n

No

Out

Port b level flag

for FIFO n

The read side FIFO level bus. Indicates how

many words are currently in the FIFO. These

status bits are synchronous to the individual read

port clocks. This status bus has one cycle of

latency.

Table 3. FIFO Partitioner Port Listing (Part 3 of 3)

Port Name

Required Direction

Direction

Comments