Altera First-In-First-Out Partitioner User Manual

Page 19

Altera Corporation

17

Getting Started

FIFO Partitioner Megafunction User Guide

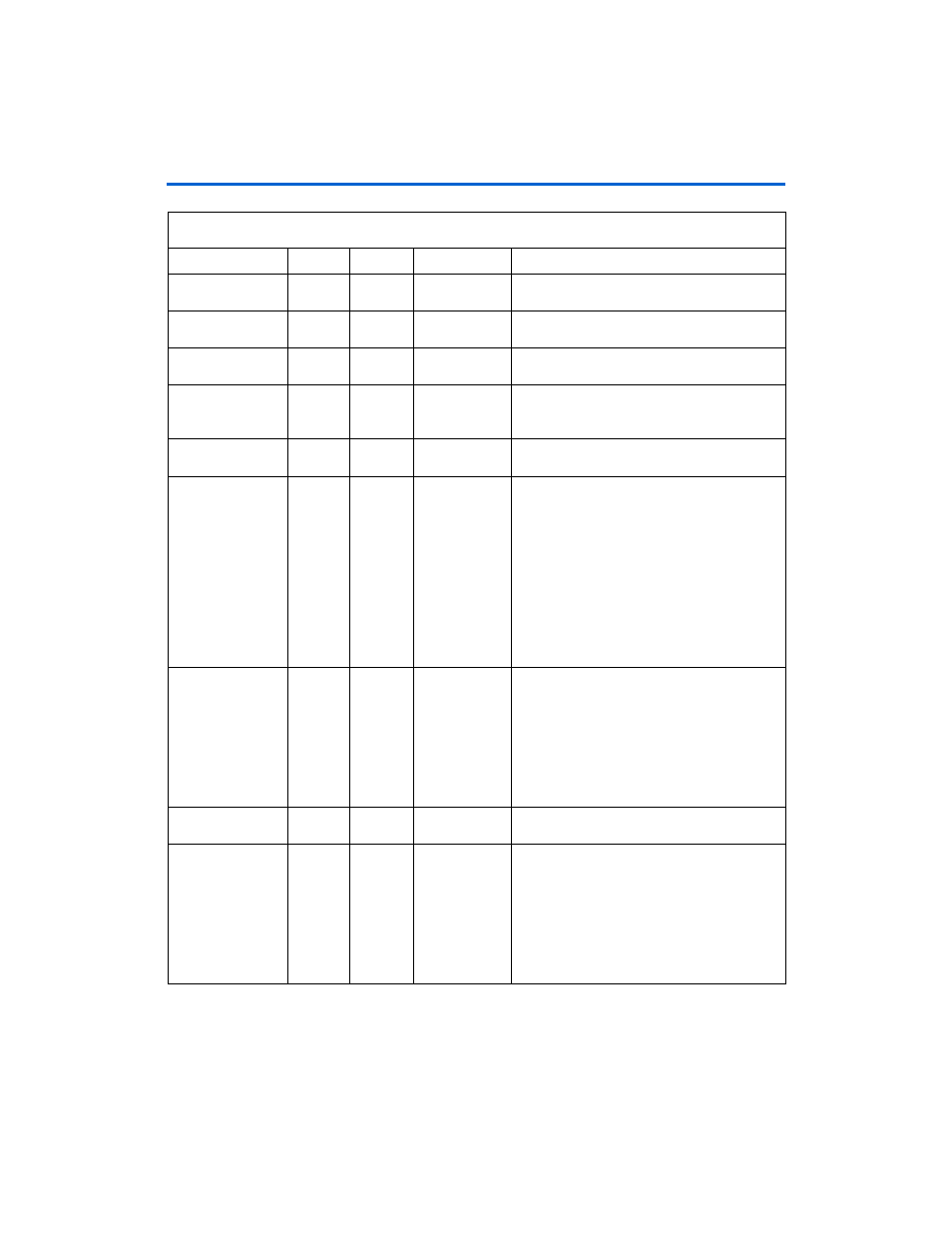

clk_port_a_n

Yes

In

Clock for port a

of FIFO n

Write side FIFO port clock. One per write port.

clk_port_b_n

Yes

In

Clock for port b

of FIFO n

Read side FIFO port clock. One per read port.

wr_data_a_n[]

Yes

In

Port a data bus

for FIFO n

Write side data port. One per write port.

wr_en_a_n

Yes

In

Port a write

enable signal for

FIFO n

One per FIFO. The user is restricted from

asserting the

wr_en_a_n

for a FIFO whose

wr_full_n

flag asserted.

rd_data_b_n[]

Yes

Out

Port b data bus

for FIFO n

One per FIFO. Behavior depends on mode of

read_b_n

signal.

read_b_n

Yes

In

Read request/

acknowledge

signal for

FIFO n

One per FIFO. The user is restricted from

asserting the

rd_en_b_n

for a FIFO whose

rd_empty_n

flag asserted. When

read_b_n

port is configured as a read acknowledge signal,

data is made available before

read_b_n

signal

is asserted, and asserting

read_b_n

signals to

the FIFO to output the contents of the next

location in the FIFO. When

read_b_n

is

configured as a read request, data becomes

available immediately after asserting

read_b_n

.

wr_full_n

Yes

Out

Port a full flag

for FIFO n

The write side FIFO full flag. This flag is

synchronous to the write port clock. The user is

restricted from asserting

wr_en_a_n

while

wr_full_n

is asserted. This flag may be

asserted for one or two clock cycles when the

FIFO is not full. To determine when the FIFO is

truly full, the user should examine this flag in

combination with the

wr_level_n

flag.

wr_empty_n

Yes

Out

Port a empty

flag for FIFO n

The write side FIFO empty flag. This flag is

synchronous to the individual write port clocks.

wr_level_n[]

No

Out

Port a level flag

for FIFO n

The write side FIFO level bus. Indicates how

many words are currently in the FIFO. These

status bits are synchronous to the write port

clocks. For FIFOs with a depth equal to a power

of two (i.e. 8, 16, 32, …), the

wr_full_n

flag is

considered the most significant bit of

wr_level_n

when

wr_level_n

= 0. This

status bus has one cycle of latency.

Table 3. FIFO Partitioner Port Listing (Part 2 of 3)

Port Name

Required Direction

Direction

Comments