Featured device: max 10 fpga, Configuration, Fpga programming over external usb-blaster – Altera MAX 10 FPGA User Manual

Page 15: Featured device: max 10 fpga –3 configuration –3

Chapter 3: Board Components

3–3

Featured Device: MAX 10 FPGA

October 2014

Altera Corporation

MAX 10 FPGA (10M08S, 144-EQFP) Evaluation Kit

User Guide

Featured Device: MAX 10 FPGA

The evaluation kit features the MAX 10 FPGA 10M08SAE144C8G device (U2) in a

144-pin Plastic Enhanced Quad Flat Pack (EQFP) package.

f

For more detailed information about the MAX 10 FPGA device family, refer to the

Configuration

The evaluation kit supports two configuration methods:

■

JTAG header (J10) for configuration by downloading a .sof file to the FPGA. Any

power cycling of the FPGA or reconfiguration will power up the FPGA to a blank

state.

■

JTAG header (J10) for programming of the on-die FPGA Configuration Flash

Memory (CFM) via a .pof file. Any power cycling of the FPGA or reconfiguration

will power up the FPGA in self-configuration mode, using the files stored in the

CFM.

FPGA Programming over External USB-Blaster

The JTAG header provides a method for configuring the FPGA (U2) using an external

USB-Blaster™, USB-Blaster II, or Ethernet Blaster download cable with the Quartus II

Programmer running on a PC. The external download cable connects to the board

through the JTAG header (J10).

Configuring the FPGA Using the Quartus II Programmer

You can use the Quartus II Programmer to configure the FPGA with a .sof. Before

configuring the FPGA, ensure that the Quartus II Programmer and the USB-Blaster

driver are installed on the host computer, the USB cable is connected to the evaluation

kit, power to the board is on, and no other applications that use the JTAG chain are

running.

1

To successfully use the USB-Blaster cable, disconnect it before power cycling the

board. After you power cycled the board, then reconnect the USB-Blaster cable.

To configure the MAX 10 FPGA FPGA, perform the following steps:

1. Start the Quartus II Programmer.

2. Click Auto Detect to display the devices in the JTAG chain.

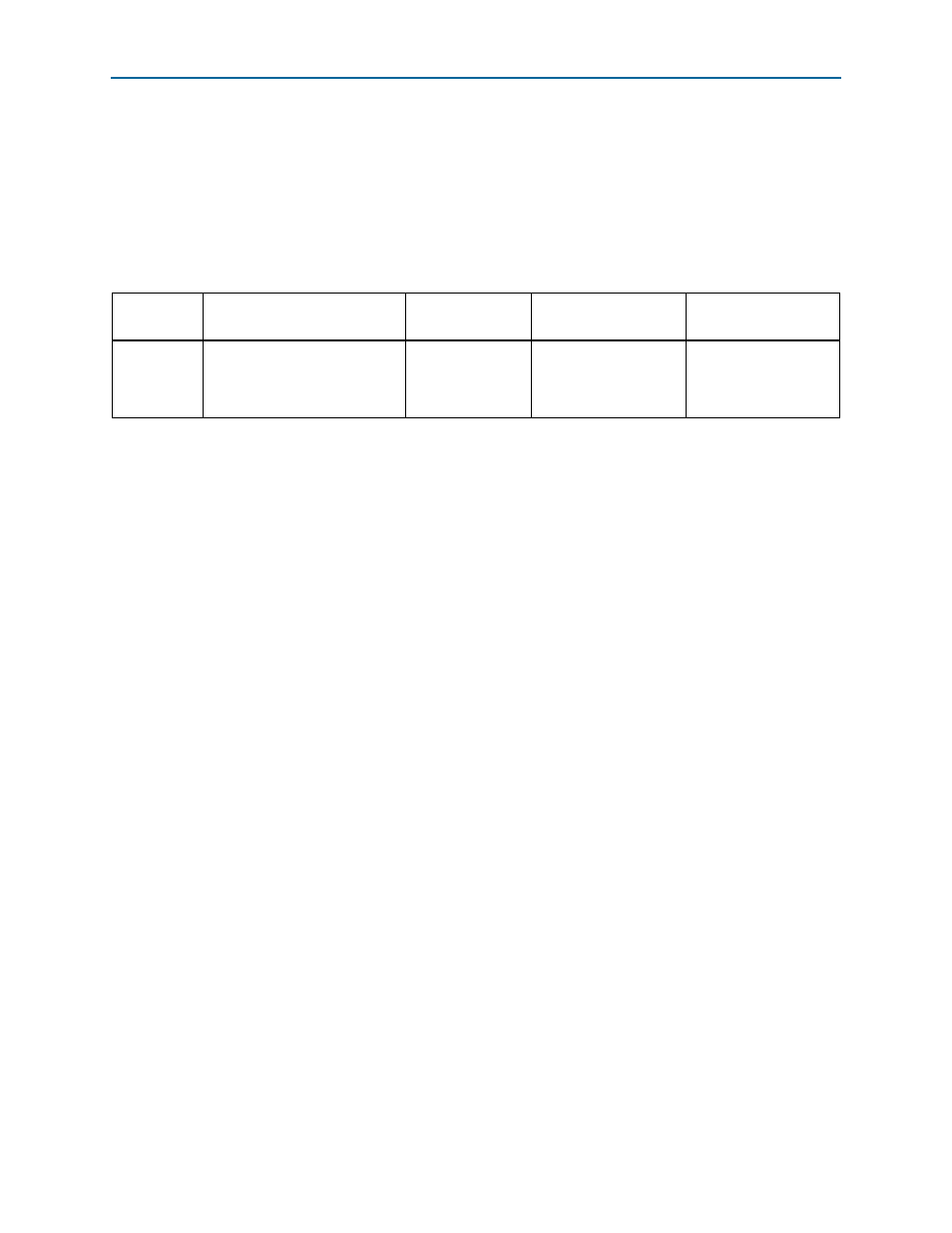

Table 3–2. MAX 10 FPGA Component Reference and Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U2

10M08SAE144C8G, (or ES

variant) Plastic Enhanced Quad

Flat Pack (EQFP), 144 pins, 20

mm x 20mm

Altera

Corporation

10M08SAE144C8GES