Post trigger counter register – ADLINK PCI-9810 User Manual

Page 35

Registers

23

Post Trigger Counter Register

The post trigger counter is a 16-bit down counter. The counter is

pre-loaded with the value in the post trigger counter register and

will count down on the rising edge of ADC sampling clock after the

trigger condition is met. When the count reaches 0, the counter

stops. The counter is used to control the delay time in delay trigger

mode and to control the post trigger sampling count in middle

trigger mode.

Address: BASE + 14h

Attribute: write only

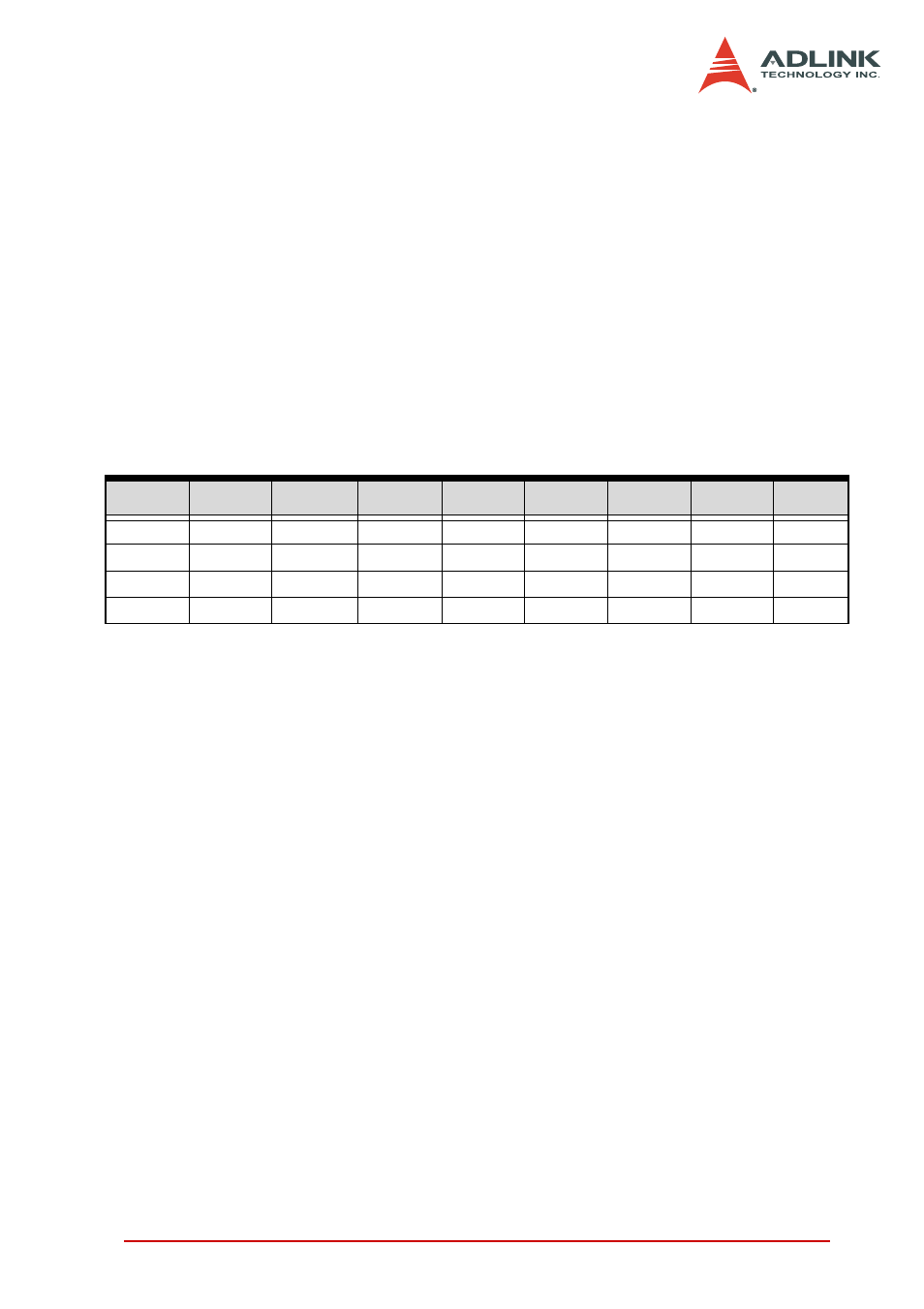

Data Format:

Bit

7

6

5

4

3

2

1

0

BASE+Ch

PSTCN 7

PSTCN 6

PSTCN 5

PSTCN 4

PSTCN 3

PSTCN 2

PSTCN 1

PSTCN0

BASE+Dh PSTCN15

PSTCN14

PSTCN13 PSTCN12

PSTCN11

PSTCN10

PSTCN9

PSTCN8

BASE+Eh

—

—

—

—

—

—

—

—

BASE+Fh

—

—

—

—

—

—

—

—

PSTCNT15...0

This value is pre-loaded to the post trigger counter when

the post trigger counter register is written.

—

Any value