Figure 3-12, Basic digitizer acquisition timing, Figure 3-12: basic digitizer acquisition timing – ADLINK PXIe-9852 User Manual

Page 37

Operations

27

PXIe-9852

from an onboard synthesizer. To achieve different sampling rates,

a scan interval counter is used.

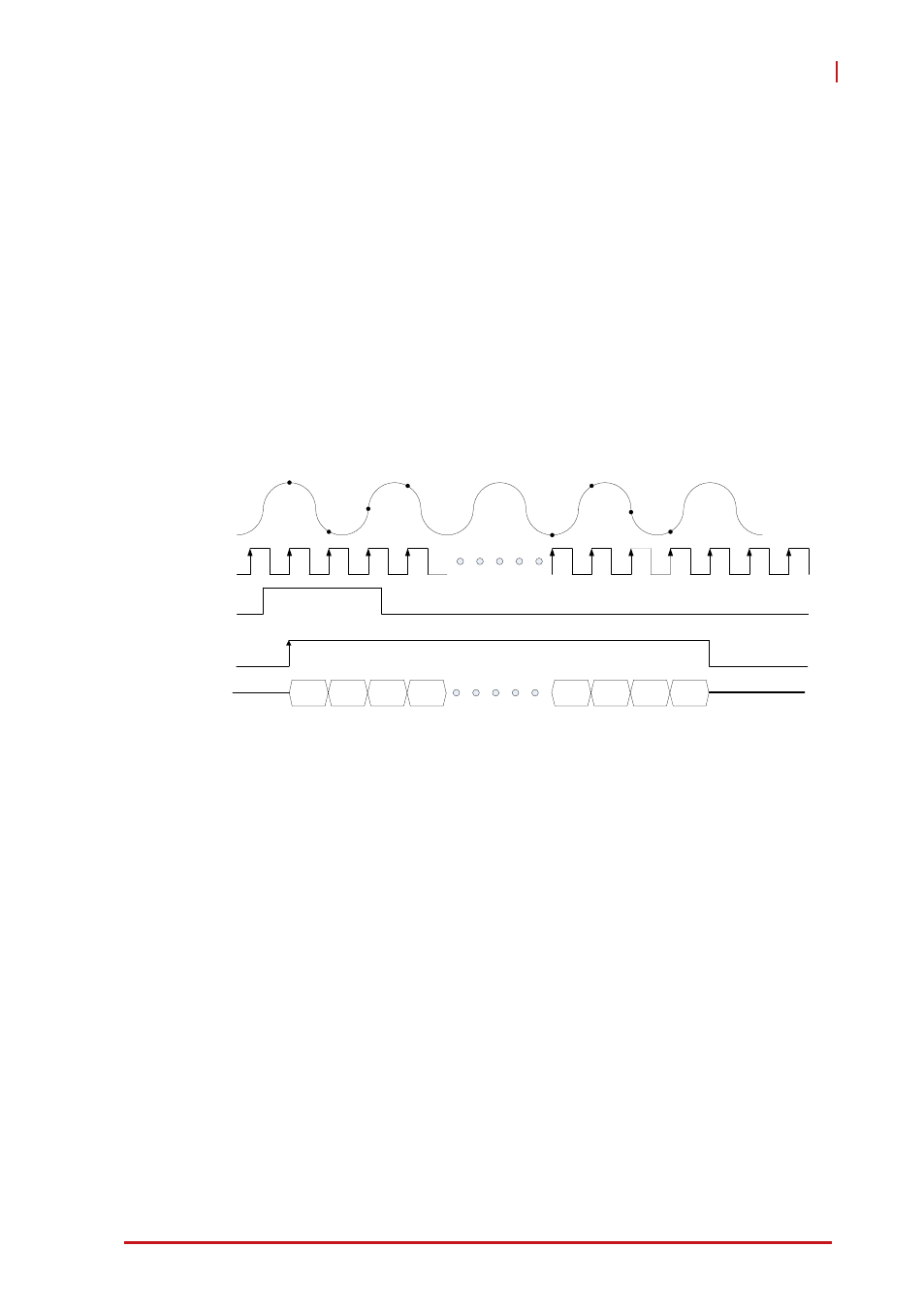

Using the post-trigger mode as an example, as shown, when a

trigger is accepted by the digitizer, the acquisition engine com-

mences acquisition of data from ADC, and stores the sampled

data to the onboard FIFO. When FIFO is not empty, data will be

transferred to system memory immediately through the DMA

engine. The sampled data is generated continuously at the rising

edge of Timebase according to the scan interval counter setting.

When sampled data reaches a specified value, in this example

256, acquisition ends.

Figure 3-12: Basic Digitizer Acquisition Timing

To achieve sampling rates other than 200MS/s, a number for scan

interval counter needs only be specified. For example, if the scan

interval counter is set as 2, the equivalent sampling rate is 200MS/

s / 2 = 100MS/s. If as 3, the equivalent sampling rate is 200MS/s /

3 = 66.66MS/s, and vice versa. The scan interval counter is 16 bits

TIMEBASE

DATA

D1

D253

D254

Acquisition

In Progress

Trigger

Acquisition initiates following this clock edge

D2

D3

D4

D255

D256

Analog

signal

Trigger mode = post-trigger, DataCnt = 256, ScanIntrv = 1