5 timebase, 1 internal reference clock, 2 external reference clock – ADLINK PXIe-9852 User Manual

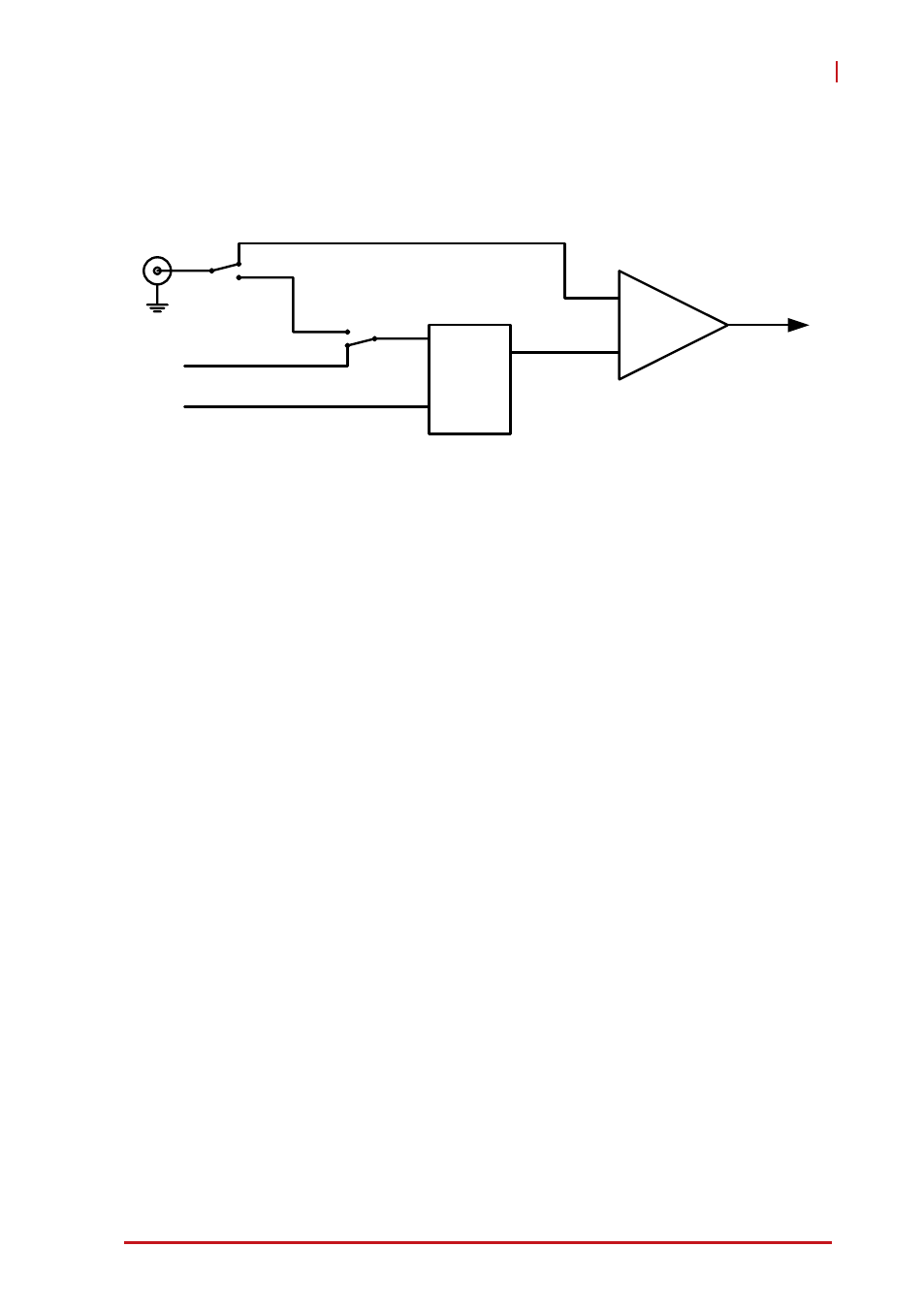

Page 35: 3 external sampling clock, Timebase, Internal reference clock, External reference clock, External sampling clock, Figure 3-10, Pxie-9852 clock architecture

Operations

25

PXIe-9852

3.5 Timebase

Figure 3-10: PXIe-9852 Clock Architecture

3.5.1

Internal Reference Clock

The PXIe-9852 internal 10MHz Crystal oscillator acts as reference

clock, generating, after synthesis, precisely 200MHz clock for

ADC.

3.5.2

External Reference Clock

The PXIe-9852 can choose an external clock source for use as a

reference clock. When an external clock reference is selected, the

synthesizer input will switch to the clock source at SMA connector

CLK IN, and generate precisely 200MHz clock for ADC. The fre-

quency of clock source is restricted to 10MHz.

3.5.3

External Sampling Clock

The PXIe-9852 can further choose an external clock source as

ADC sampling clock. When an external sampling clock is selected,

the ADC sampling frequency switches to the clock source at SMA

Connector CLK IN, and clock source frequency is available from

40MHz to 200MHz.

Synthesizer

CLK Buffer

PXIe 10MHz / Xtal 10MHz

PXIe 100MHz

To ADC

CLK IN

External Sampling CLK

External Reference CLK