Table 1-5: pxie-9852 i/o array legend – ADLINK PXIe-9852 User Manual

Page 20

10

Introduction

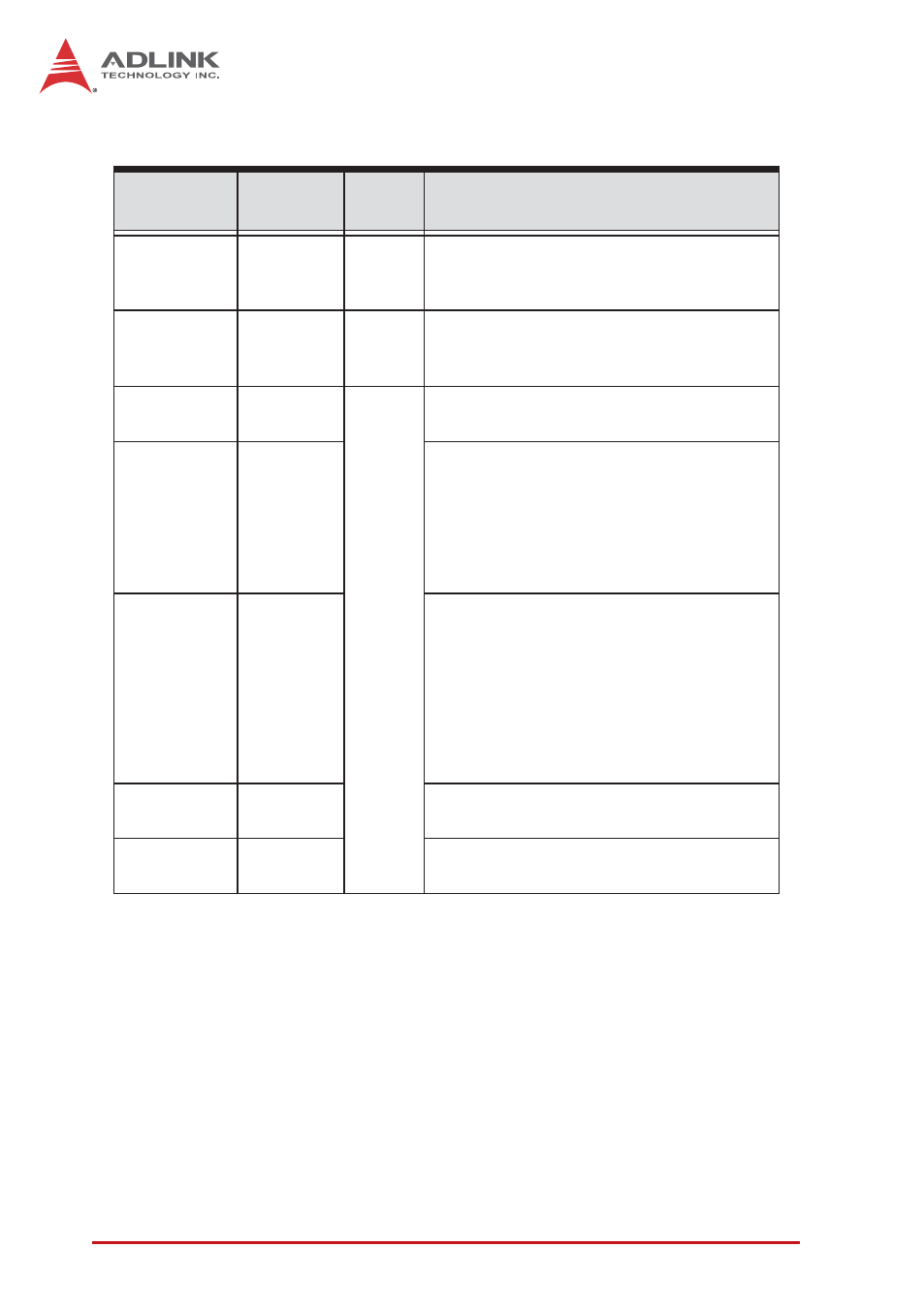

Table 1-5: PXIe-9852 I/O Array Legend

Name

Faceplate

Legend

Type

Remark

CH0

N/A

Blue

On indicates CH0 acquisition ongoing

Off indicates CH0 acquisition stopped

CH1

N/A

Blue

On indicates CH1 acquisition ongoing

Off indicates CH1 acquisition stopped

Ext. Clock

Input

CLK IN

SMA

Screw

Input for external reference clock or

sample clock to digitizer

Ext. Digital

Trigger

Input

TRG IN

External digital trigger input, receiving

trigger signal from external instrument

and initiating acquisition

Trigger

Output

TRG OUT

Trigger output, in which every time

acquisition begins, a pulse

synchronized with Timebase clock

asserts and is output through this

connector, at pulse width

programmable from 50ns to 10μs via

software

Analog

Input

CH0

Analog input channel

Analog

Input

CH1

Analog input channel

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (83 pages)

- cPCI-7300 (82 pages)