Counter #1, Counter #2, Counter #3 – ADLINK ACL-8454/12 User Manual

Page 22: Counter #4, Counter #5, Counter #6, Counter #7, Counter #8, Counter #9, Counter #10

14

• Installation & Configurations

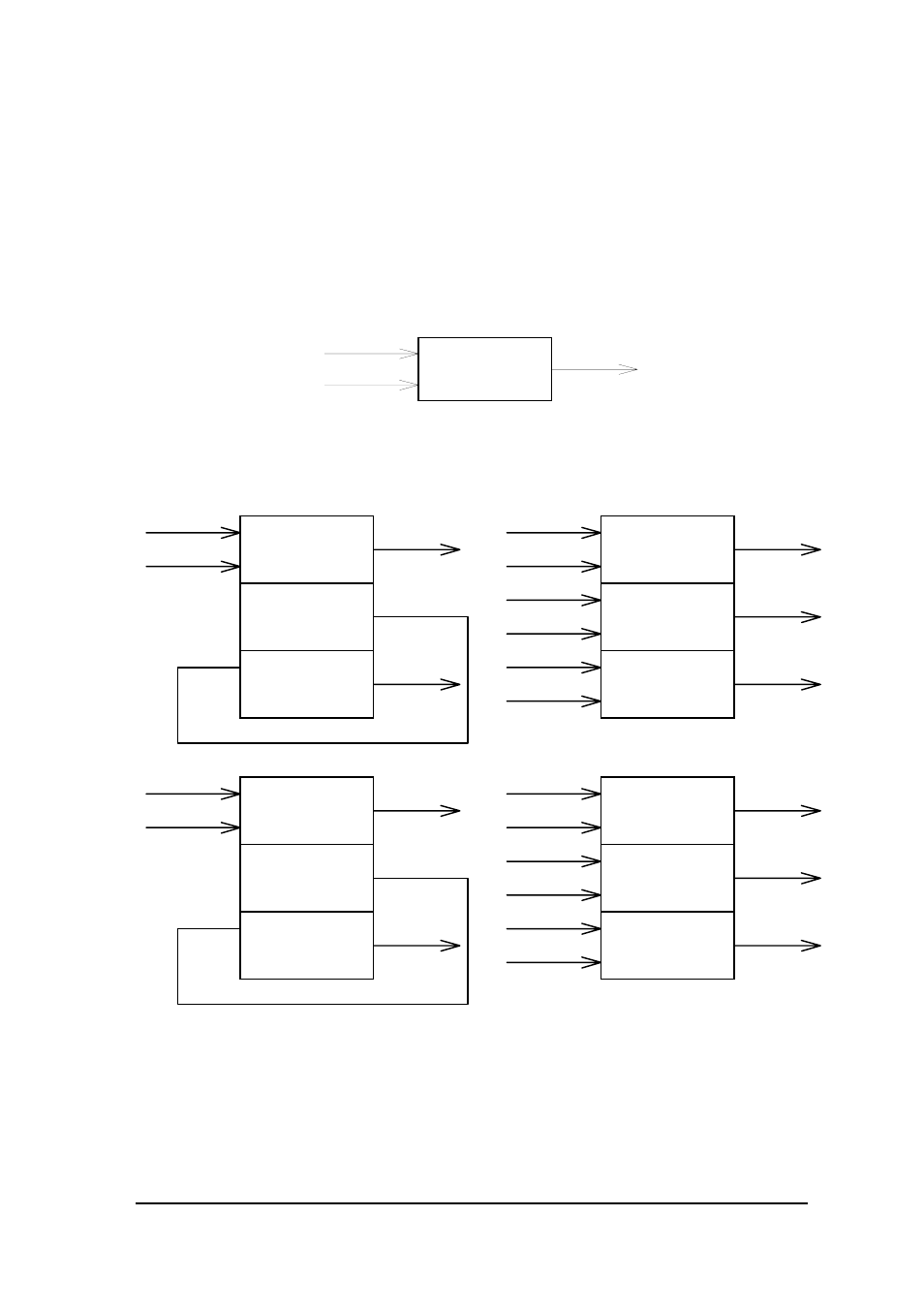

There are three signals (2 input,1 output) for each counter, a clock input

signal, a gate control signal, and an output signal. The Figure 2.7 illustrates

the block diagram of the 8254 counter. CLK1 ~ CLK12 are clock sources

and GATE1 ~ GATE12 are gate control signals. The COUT1 ~ COUT12

are outputs of the counters. The Figure 2.8 shows all the labels and the

inter-connection of the 8254 counters when all the 4 chips are installed. The

COUT5 and COUT11 are used only for internal.

Clock Source Input

Counter / Timer Output

Gate Control Input

Counter

8254 Chip

C

G

O

Figure 2.7 Block Diagram of the 8254 Counter

CLK1

COUT1

GATE1

Counter #1

CLK2

COUT2

GATE2

Counter #2

CLK3

COUT3

GATE3

Counter #3

8254 Chip #1

CLK4

COUT4

GATE4

Counter #4

1 MHz

COUT5

Counter #5

COUT5

COUT6

Counter #6

8254 Chip #2

CLK7

COUT7

GATE7

Counter #7

CLK8

COUT8

GATE8

Counter #8

CLK9

COUT9

GATE9

Counter #9

8254 Chip #3

CLK10

COUT10

GATE10

Counter #10

COUT11

COUT11

COUT12

Counter #12

8254 Chip #4

Counter #11

C

G

O

C

G

C

G

C

G

C

G

C

G

C

G

C

G

C

G

C

G

C

G

C

G

O

O

O

O

O

O

O

O

O

O

O

'H'

'H'

'H'

'H'

1M Hz

Figure 2.8 Counters Architectural