7 clock system – ADLINK ACL-8454/12 User Manual

Page 19

Installation & Configurations

• 11

2.7 Clock

System

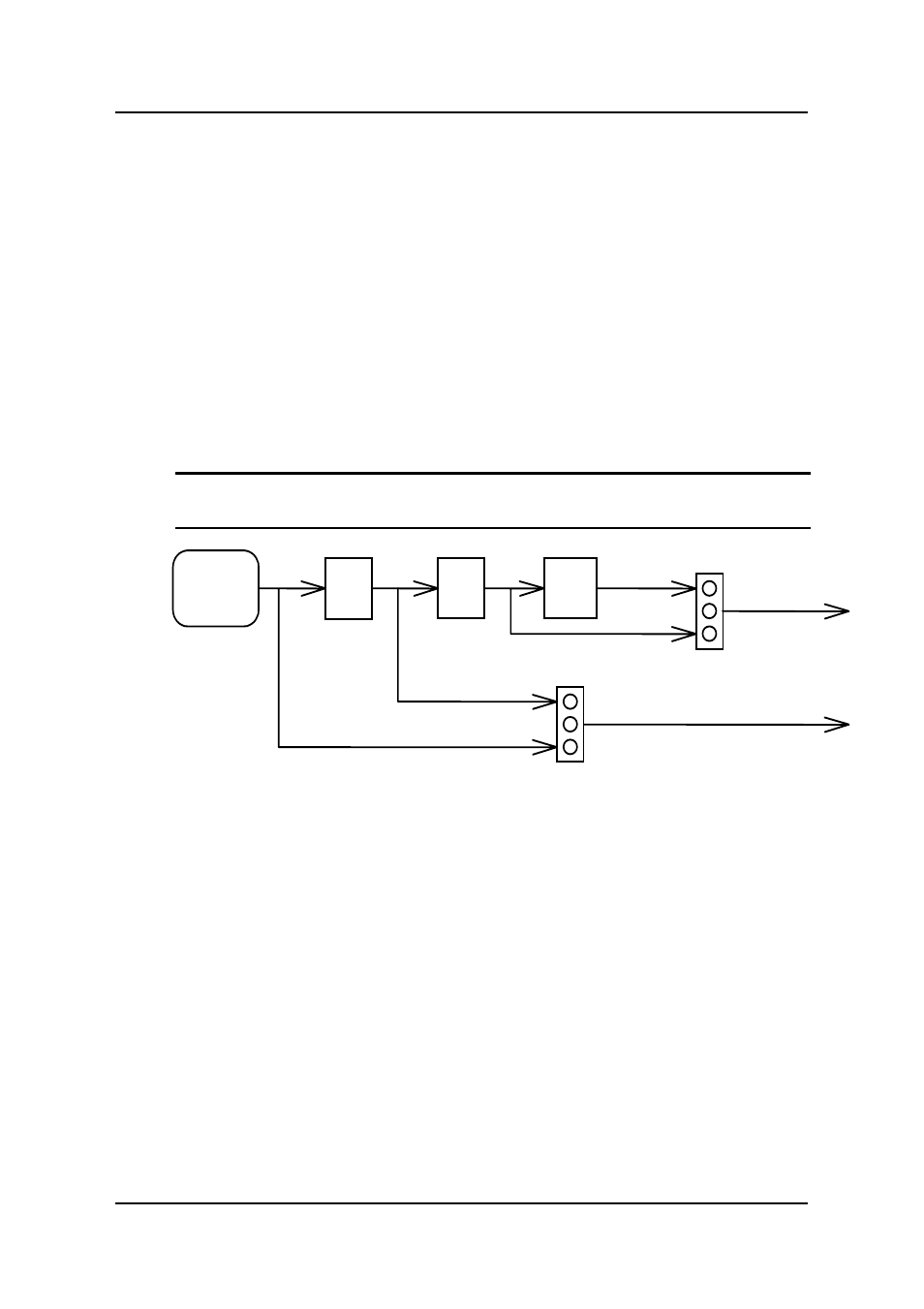

The clock system of ACL-8454 provides the internal clock source for the

8254 chips. The block diagram of the clock system is shown in the Figure

2.4. Two clock sources, which named as CLOCK1 and CLOCK2, are

divided from the internal 10Mhz signal. The clock of every counter/timer can

be one of the 4 sources: CLOCK1, CLOCK2, external clock source or

cascaded source from the ‘last’ channel. Refers to next section for details

of setting clock for each counter/timer.

The crystal on ACL-8454 is 10 MHz which is the highest frequency of the

card. The maximum speed of the 8254 chips can run under 10 MHz. As

users plug the lower speed 8254 chips into ACL-8454, the lower frequency

clock source should be used. A frequency divider is used to generate 2MHz

for such circumstance.

Note: Certain versions of 8254 or 8253 chips, such as 8254-5, can

run under only 2 MHz.

OSC

10 MHz

2M Hz

10M Hz

CLOCK1

CLOCK2

100K Hz

1M Hz

ч5

ч10

ч2

Figure 2.4 Clock system of ACL-8454