ADLINK PCI-8554 User Manual

Page 27

Getting Started •17

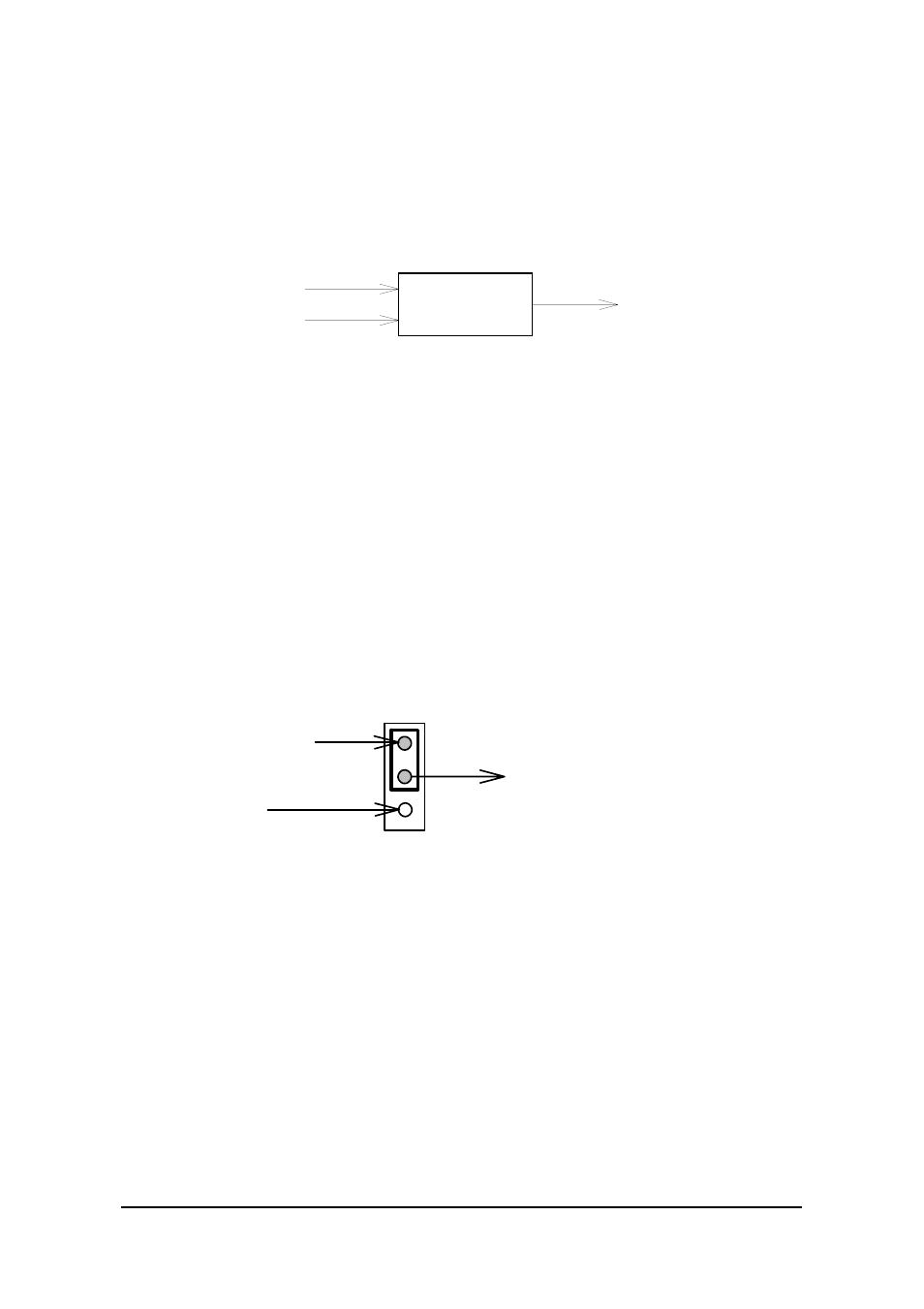

2.9.1 Independent Counters (Counter 1~10)

Counters 1 to 10 are independent counters because the clock source and

gate control of those counters can be set independently (Thus named

Independent Counter).

CLK1

COUT1

GATE1

Counter #1

8254 Chip #1

C

G

O

Figure 8: Example of ‘independent counters’

2.9.2 Cascaded

Counters

The connection of Counter 11 and 12 are different from the independent

counters. These two counters are cascaded counters by default settings.

The clock source of counter 11 is set to the internal 8 MHz clock by JP12,

while JP13 connects its output to counter 12. In fact, counter 11and 12

are designed for frequency division by using the 8254's square wave

generator mode. The gates of these counters are by default tied to logic

high (‘H’) to enable these counters at all times. Users can change JP14

and JP15 to tie the signal to the GATE pins.

Gate of Counter

#11 / #12

GATE11/12

Vcc

JP14 / JP15

Figure 9: JP14/JP15 (For cPCI-8554/R only)

COUT12 can precisely generate frequencies up to 2MHz and as low as

0.00186 Hz. Note that the COUT12 signal can also be used as an

interrupt source. See ‘Interrupt Sources’ section for details. Figure 10

illustrates the cascaded counters - counters 11 and 12. Sometimes, you

may require all 12 counters to operate independently. For such a case,

you can break the default connection by reconfiguring jumpers J12 and

J13. Note that both counters 11 and 12 only have 2 selectable clock

sources. It can be either the 8 MHz internal clock source or an external

clock source.