ADLINK cPCI-9116 User Manual

Page 55

Operation Theory

• 45

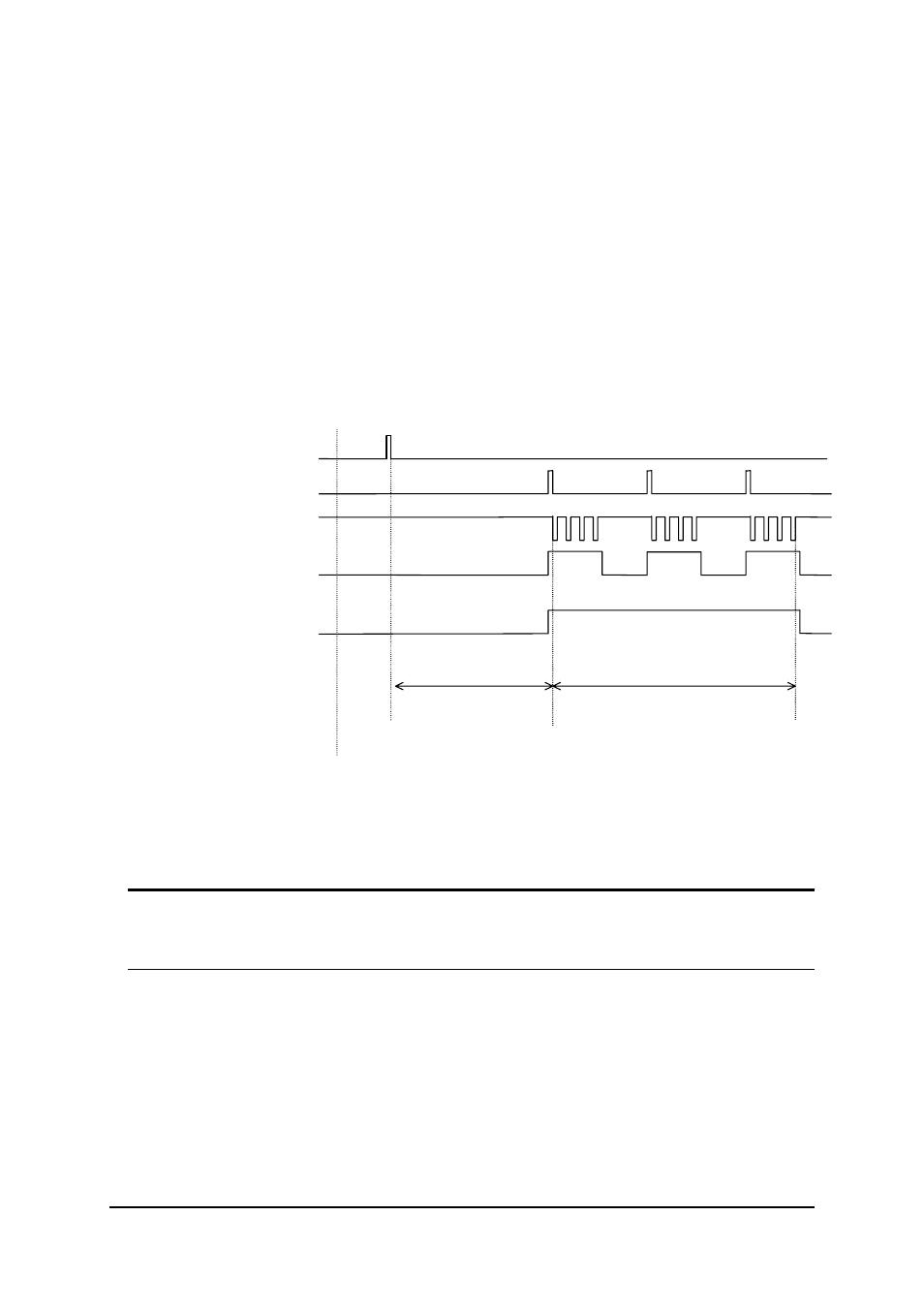

Delay Trigger Acquisition

Use delay trigger acquisition in applications where you want to delay the data

collection after the occurrence of a specified trigger event. The delay time is

controlled by the value, which is pre-loaded in the Delay_counter (16bit). The

counter counts down on the rising edge of Delay_counter clock source after

the trigger condition is met. The clock source can be software programmed

either Timebase clock (24MHz) or A/D sampling clock (Timebase

/SI2_counter). When the count reaches 0, the counter stops and 9116 card

starts to acquire data. The total acquired data length = DIV_counter *

SC_counter.

(DIV_Counter=4, SC_Counter=3)

Acquisition_in_progress

Scan_start

AD_conversion

Scan_in_progress

(SSH_OUT)

Acquired & stored data

(3 scans)

Operation start

ExtTrg

Delay until

Delay_Counter

reaches 0

Figure 17: Delay trigger

Note:

When the Delay_counter clock source is set to Timebase, the maximum

delay time = 2

16

/24M s = 2.73ms, and when the source is set to A/D

sampling clock, the maximum delay time = 2

16

* SI2_counter / 24M).