Solvline Eddy Series Ver 2.1a User Manual

Page 30

Chapter 3. Hardware Description

Pin

Signal

Description

1,2

VCC

3.0 ~ 5.5V DC input

3

NTRST

Test Reset Signal

4

TDI

Test Data In

5 TCK

Test

Clock

6 TDO

Test

Data

Out

7

TMS

Test Mode Select

8

NRST

Reset signal for external devices

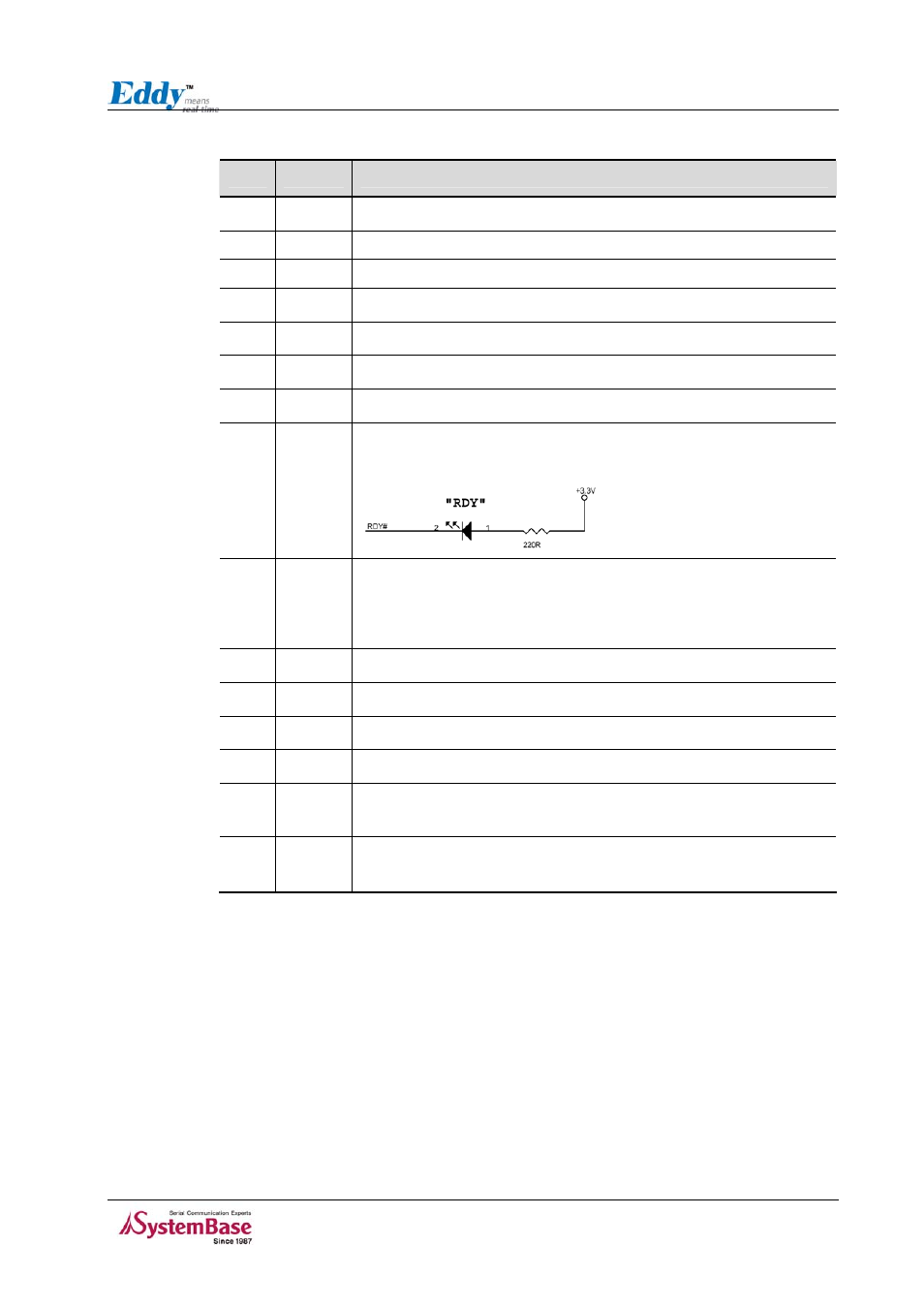

9 RDY#

Ready indicator (Active low output)

Processor status can be indicated, when connected as below.

10 nRESET

Connection to external reset switch (Input)

As reset logic is built-in, this pin can be connected directly to the

switch without any additional circuit. When pressing the switch

for more than 5 seconds (low input), factory default settings are

restored.

11 GND

Ground

12 GND

Ground

13

GPIO0

Programmable I/O 0 (user-defined I/O)

14

GPIO1

Programmable I/O 1 (user-defined I/O)

15

GPIO2

Programmable I/O 2 (user-defined I/O)

16

GPIO3

Programmable I/O 3 (user-defined I/O)

3-5