Chapter 3. hardware description, 1 eddy-cpu, Chapter 3 – Solvline Eddy Series Ver 2.1a User Manual

Page 16: Hardware description -1, 1 eddy-cpu -1, Chapter 3 . hardware descriptions, Explains the layout

Chapter 3. Hardware

Description

3-1

Chapter 3.

Hardware Description

This chapter provides Eddy’s hardware information, including block diagram, layout, pin specifications,

dimensions and other hardware-related issues.

3.1 Eddy-CPU

Ethernet port is provided as pin headers, and the transformer and RJ-45 connector should be manually

implemented by users. (RJ-45 connector with embedded transformer, normally called LAN-Mate or

MAC Jack, can be used as a simpler approach.

16 bit address / 8 bit data bus provides flexibility in external peripheral connectivity and up to 16

programmable IO can be used on user’s side.

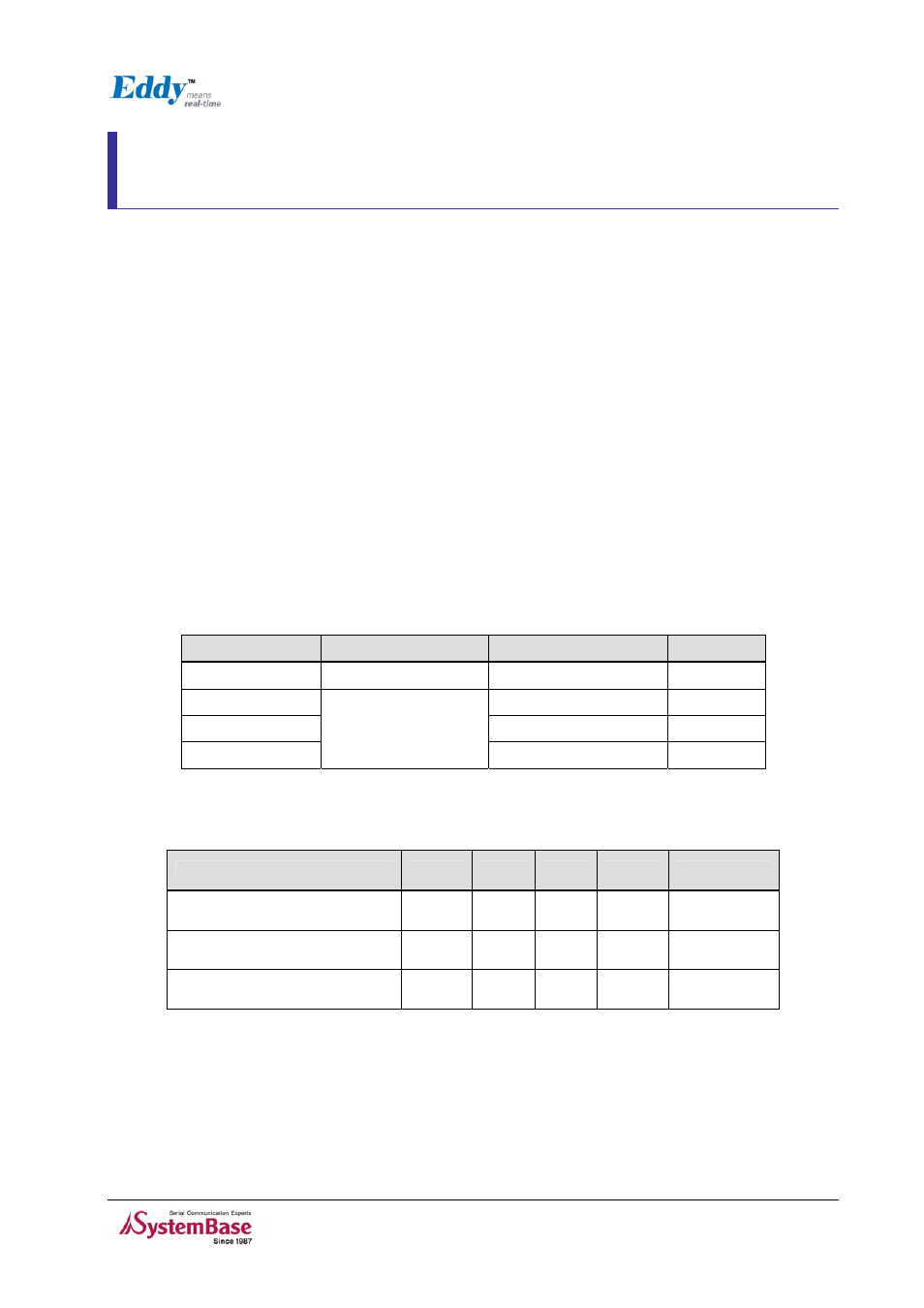

Chip Selects

Chip select signal Typical Slave Device

Address Range

Size

NCS0 Flash

ROM 0x10000000~x107FFFFF

4MB

NCS2 0x30000000~

NCS6 0x60000000~

NCS7

Application

dependent

0x70000000~

Eddy-CPU Operating Conditions

Parameter

Symbol

Min

Typ

Max

Units

Supply Voltage

Vcc

3.0

3.3

3.6

VDC

Supply Current

Icc

300

mA

Operating ambient

temperature

T

A

-40

85

℃