Solvline Eddy Series Ver 2.1a User Manual

Page 21

Chapter 3. Hardware Description

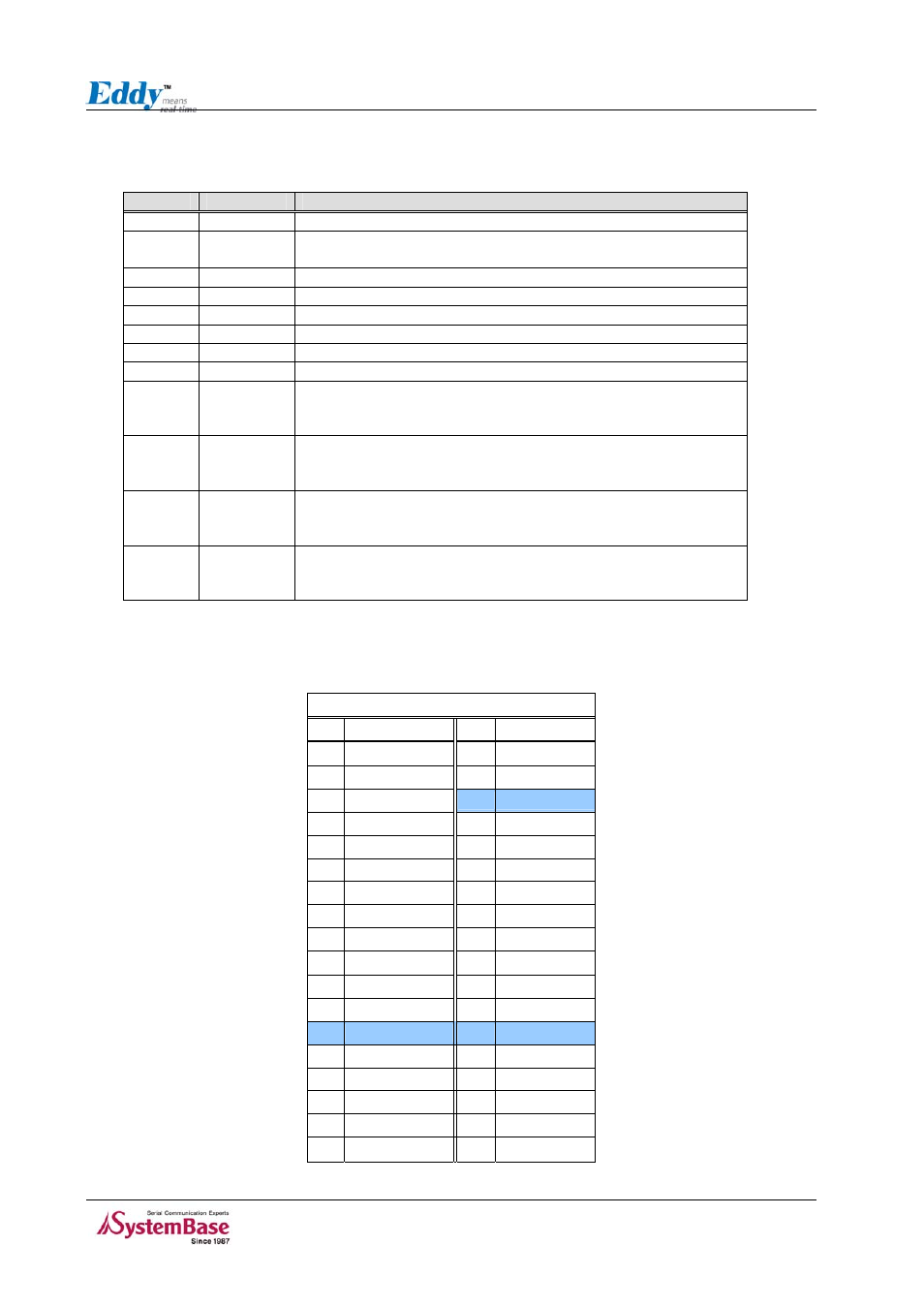

J2 Pin Description

Pin No

Name

Description

1~16

A[15:0]

Address Bus 0~15

17 NCS2

External device Chip Select signal, 256MB memory area

addressable, active low

18

NWE

External device Write Enable signal, active low

19

HRST

External device Reset signal, active high

20

NRD

External device Read signal

21, 23

GND

Ground

22, 24

3.3V

3.0V to 3.6V power input

25~32 D[7:0]

Data

Bus

33 NCS6/FIQ

- External device Chip Select signal, 256MB memory area

addressable, active low

- Fast Interrupt Input

34 JTAGSEL

JTAG boundary scan can be used by connecting pin34 and 36.

This pin should not be connected when using ICE(In-Circuit

Emulator) or in normal operation status.

35 NCS7/IRQ0

- External device Chip Select signal, 256MB memory

addressable, active low

- External Interrupt Input

36 VDDBU

JTAG boundary scan can be used by connecting pin34 and 36.

This pin should not be connected when using ICE(In-Circuit

Emulator) or in normal operation status.

J3 Specifications

J3

Pin Desc. Pin

Desc.

1 PID0

2 PID1

3 PID2

4 PID3

5 PID4

6

GND

7 GPIO1

8 GPIO2

9 GPIO3

10

GPIO4

11 GPIO5 12

GPIO6

13 GPIO7 14

GPIO8

15 GPIO9 16

GPIO10

17 GPIO11 18

GPIO12

19 GPIO13 20

GPIO14

21 GPIO15 22

GPIO16

23 DRXD 24

DTXD

25

GND

26

GND

27 BMS 28

NRST

29 DCD 30

RXD

31 TXD 32

DTR

33 DSR

34

RTS

35 CTS 36

RI

3-6