Switching characteristics – Cypress Perform CY7C136A User Manual

Page 5

CY7C132, CY7C136

CY7C136A, CY7C142, CY7C146

Document #: 38-06031 Rev. *E

Page 5 of 15

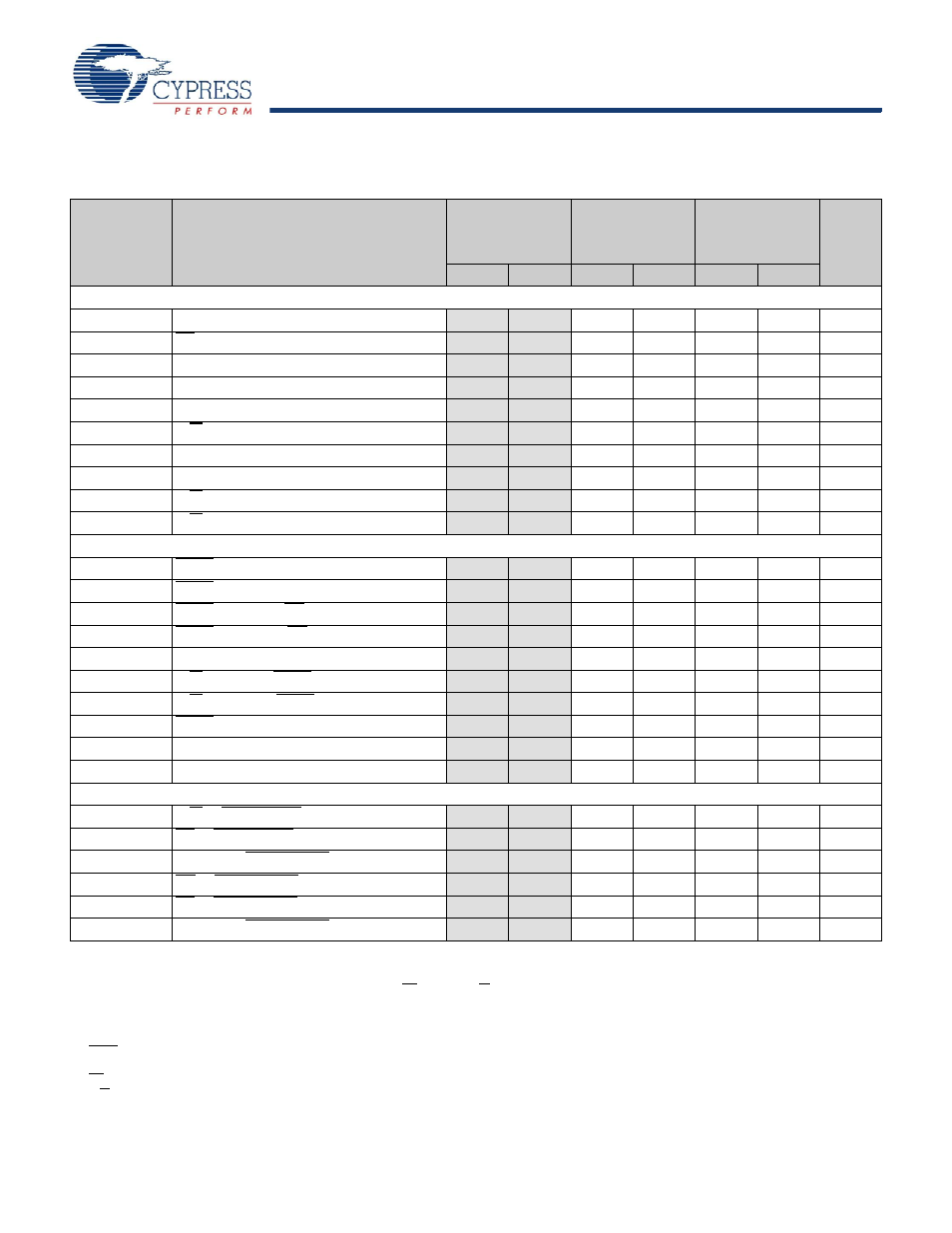

Write Cycle

t

WC

Write Cycle Time

15

25

30

ns

t

SCE

CE LOW to Write End

12

20

25

ns

t

AW

Address Setup to Write End

12

20

25

ns

t

HA

Address Hold from Write End

2

2

2

ns

t

SA

Address Setup to Write Start

0

0

0

ns

t

PWE

R/W Pulse Width

12

15

25

ns

t

SD

Data Setup to Write End

10

15

15

ns

t

HD

Data Hold from Write End

0

0

0

ns

t

HZWE

R/W LOW to High Z

10

15

15

ns

t

LZWE

R/W HIGH to Low Z

0

0

0

ns

Busy/Interrupt Timing

t

BLA

BUSY LOW from Address Match

15

20

20

ns

t

BHA

BUSY HIGH from Address Mismatch

15

20

20

ns

t

BLC

BUSY LOW from CE LOW

15

20

20

ns

t

BHC

BUSY HIGH from CE HIGH

15

20

20

ns

t

PS

Port Set Up for Priority

5

5

5

ns

t

WB

R/W LOW after BUSY LOW

0

0

0

ns

t

WH

R/W HIGH after BUSY HIGH

13

20

30

ns

t

BDD

BUSY HIGH to Valid Data

15

25

30

ns

t

DDD

Write Data Valid to Read Data Valid

Note 15

ns

t

WDD

Write Pulse to Data Delay

Note 15

ns

Interrupt Timing

t

WINS

R/W to INTERRUPT Set Time

15

25

25

ns

t

EINS

CE to INTERRUPT Set Time

15

25

25

ns

t

INS

Address to INTERRUPT Set Time

15

25

25

ns

t

OINR

OE to INTERRUPT Reset Time

15

25

25

ns

t

EINR

CE to INTERRUPT Reset Time

15

25

25

ns

t

INR

Address to INTERRUPT Reset Time

15

25

25

ns

Shaded areas contain preliminary information.

Switching Characteristics

Over the Operating Range (Speeds -15, -25, -30)

[8]

(continued)

Parameter

Description

7C136-15

[4]

7C146-15

7C132-25

[4]

7C136-25

7C142-25

7C146-25

7C132-30

7C136-30

7C142-30

7C146-30

Unit

Min

Max

Min

Max

Min

Max

Notes

12. The internal write time of the memory is defined by the overlap of CE LOW and R/W LOW. Both signals must be LOW to initiate a write and either signal can terminate

a write by going HIGH. The data input setup and hold timing must be referenced to the rising edge of the signal that terminates the write.

13. These parameters are measured from the input signal changing, until the output pin goes to a high impedance state.

14. CY7C142/CY7C146 only.

15. A write operation on Port A, where Port A has priority, leaves the data on Port B’s outputs undisturbed until one access time after one of the following:

BUSY on Port B goes HIGH.

Port B’s address toggled.

CE for Port B is toggled.

R/W for Port B is toggled during valid read.

16. 52-pin PLCC and PQFP versions only.