Spartan-6 ddr2 – Digilent 410-256P-KIT User Manual

Page 4

FMC Carrier-S6 Reference Manual

www.digilentinc.com

page 4 of 7

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

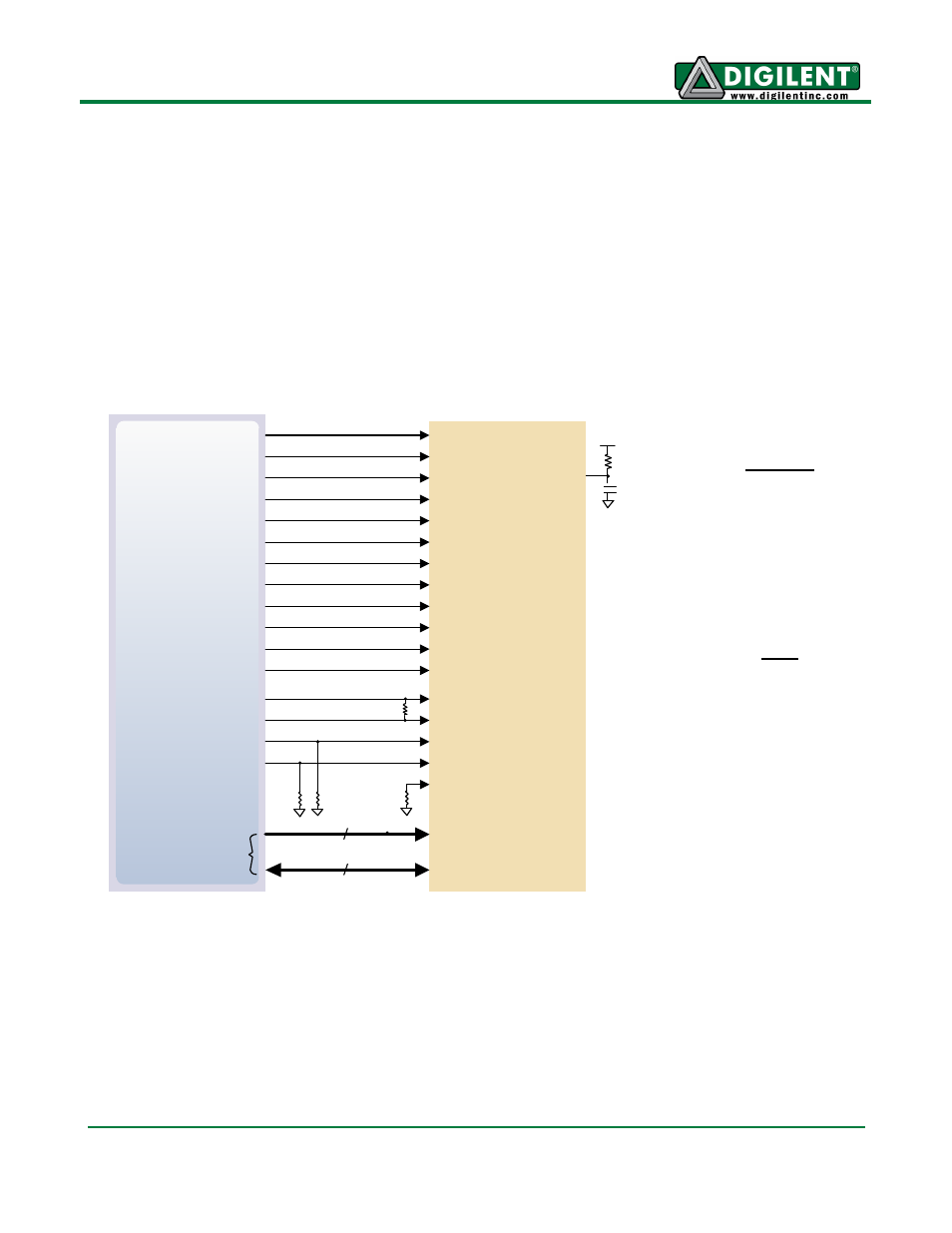

DDR2 Memory

A single 1Gbit DDR2 memory chip is driven from the memory controller block in the Spartan-6

FGPA. The DDR2 device, a Micron MT47H64M16-25E or equivalent, provides a 16-bit bus and 64M

locations. The FMC Carrier - S6 board has been tested for DDR2 operation at up to an 800MHz data

rate.

The DDR2 interface follows the pinout and routing guidelines specified in the Xilinx Memory Interface

Generator (MIG) User Guide. The interface supports SSTL18 signaling, and all address, data, clocks,

and control signals are delay-matched and impedance-controlled. Address and control signals are not

terminated. Two well-matched DDR2 clock signal pairs are provided so the DDR can be driven with

low-skew clocks from the FPGA.

Address

A12: G6

A4: F3

A11: D3

A3: L7

A10: F4

A2: H5

A9: D1

A1: J6

A8: D2

A0: J7

A7: H6

A6: H3

A5: H4

Data

D15: U1

D7: J1

D14: U2

D6: J3

D13: T1

D5: H1

D12: T2

D4: H2

D11: N1

D3: K1

D10: N2

D2: K2

D9: M1

D1: L1

D8: M3

D0: L2

DQ[15:0]

13

16

AD[12:0]

RAS#

CAS#

WE#

BA0

BA1

BA2

See Table

CS#

L4

P1

P2

E1

F1

F2

E3

K5

L5

Spartan-6

DDR2

VREF

CKE

CK

CK#

UDQS_P

UDQS_N

LDQS_P

LDQS_N

UDM

LDM

ODT

1V8

L3

K4

K3

K6

H7

G1

G3