Application examples – Digilent 210-251P-BOARD User Manual

Page 6

JTAG-SMT2 Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 6 of 11

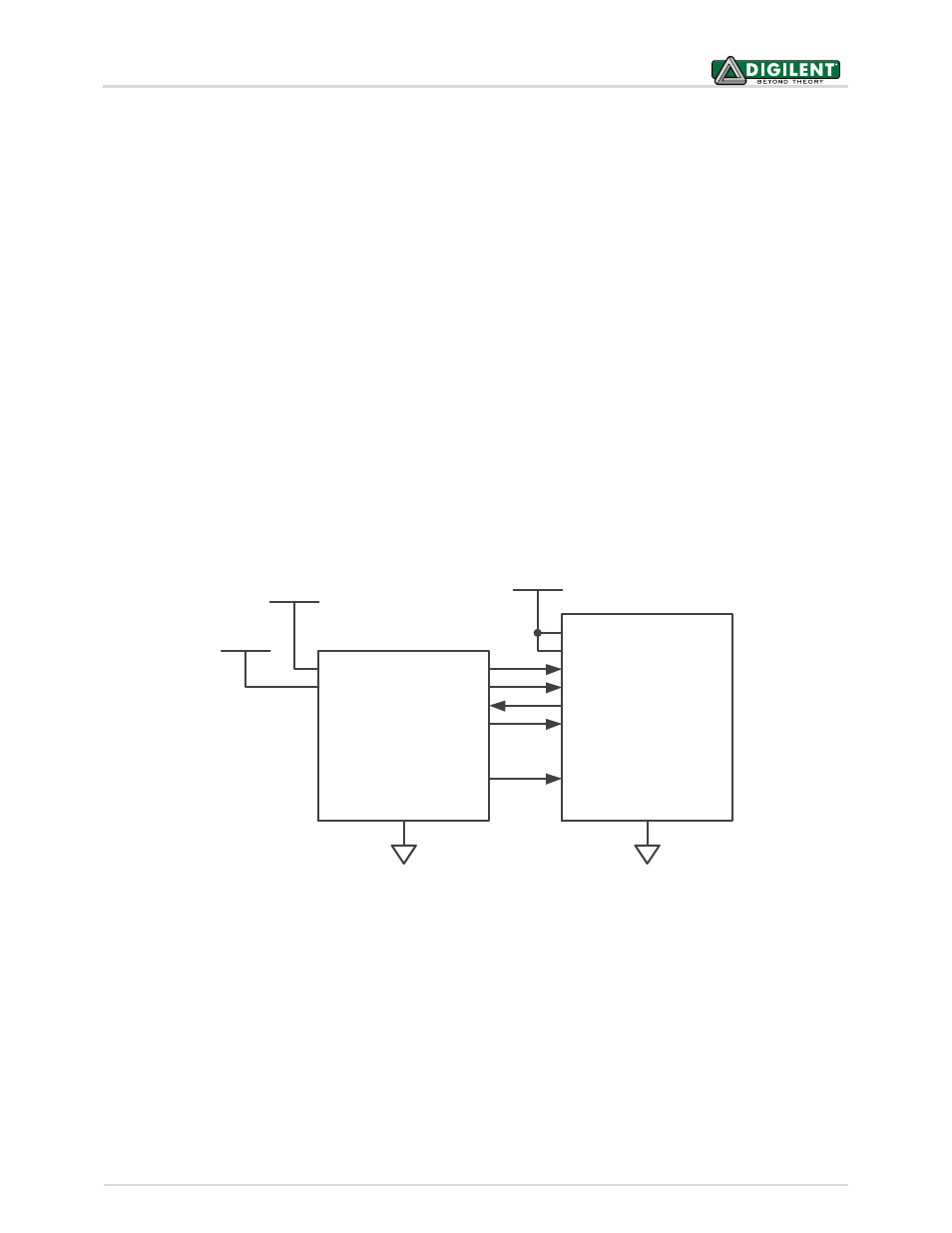

When customers use the JTAG-SMT2 to interface the scan chain of Xilinx’s Zynq platform, they should connect the

GPIO2 pin of the SMT2 to the Zynq’s PS_SRST_B pin. This connection allows the Xilinx Tools to reset the Zynq’s

processor core at various times during debugging operations. Please see the following “Application Examples”

section for more information.

Note: The Xilinx tools expect GPIO2 to be connected to the SRST_B pin on a Zynq chip. As a result, GPIO2 may not be

used as a general purpose I/O if the Xilinx Tools are going to be used to communicate with the SMT2.

Note: DPIO port 0 can only be used while both JTAG and SPI are disabled.

Application Examples

Example 1:

Interfacing a Zynq-7000 when VCCO_0 and VCCO_MIO1 use a common supply

Figure 9demonstrates how to connect the JTAG-SMT2 to Xilinx’s Zynq-7000 silicon when the same voltage supplies

both the VCCO_0 (Programmable Logic Bank 0 Power Supply) and the VCCO_MIO1 (Processor MIO Bank 1 Power

Supply).

In this case the SMT2 has a 100K pull-up to VREF, which operates at the same voltage as VCCO_MIO1. This similar

voltage makes it possible to eliminate the external pull-up that is normally required for the PS_SRST_B pin.

VCCO_0

VCCO_MIO1

PS_SRST_B

ZYNQ-

7000

TDO

TMS

TDI

TCK

GND

VDD

VREF

TDO

JTAG-

SMT2

GND

TMS

TDI

TCK

GPIO0

GPIO1

GPIO2

VCCO

3.3V

VCCO

Figure 9. Connecting the JTAG-SMT2 to Xilinx’s Zynq-7000.