Gpio pins – Digilent 210-251P-BOARD User Manual

Page 5

JTAG-SMT2 Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 5 of 11

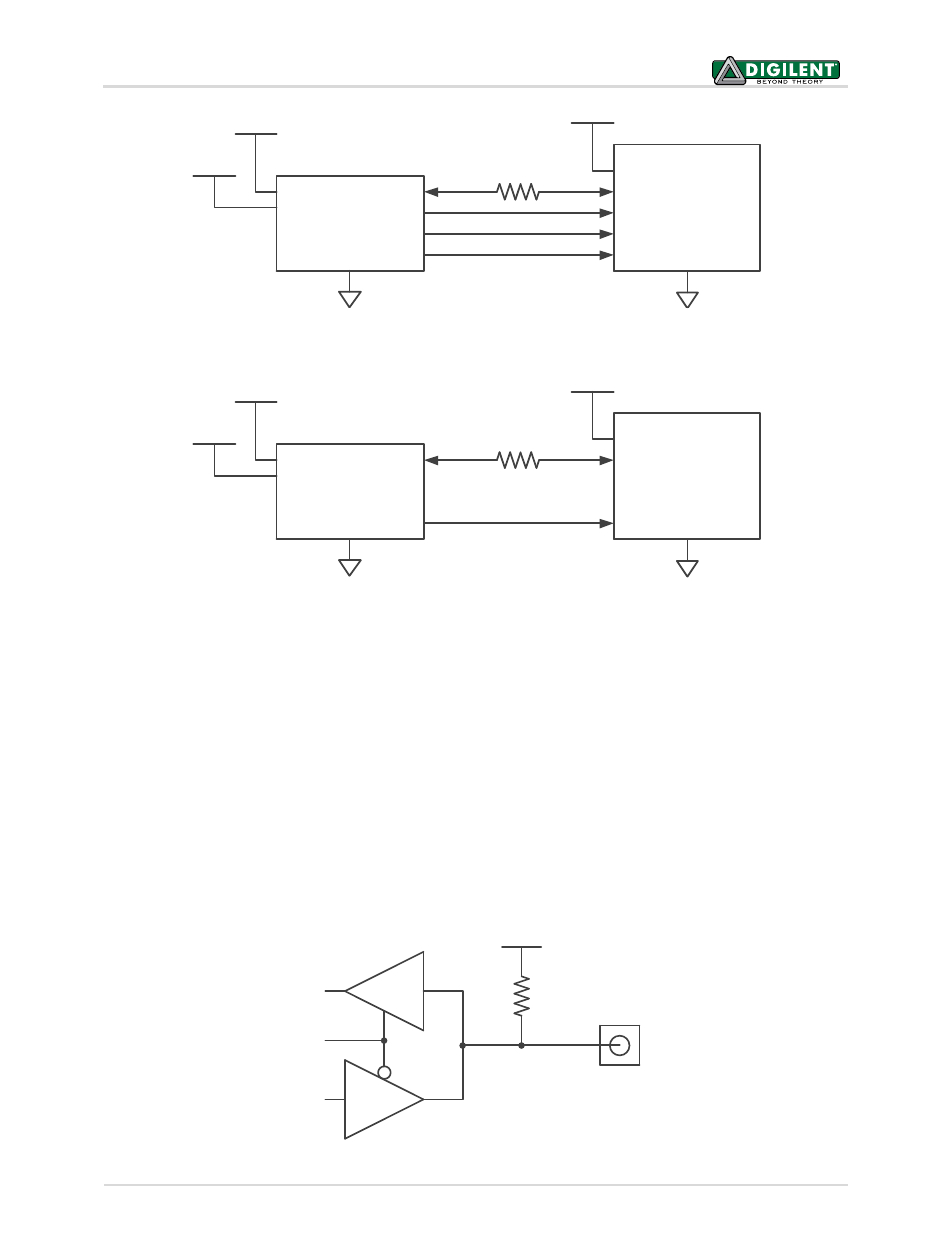

VIO

1149.7

Target

System

TDOC

TMSC

TDIC

TCKC

GND

VDD

VREF

TDO

JTAG-

SMT2

GND

TMS

TDI

TCK

VIO

3.3V

VIO

200

VIO

1149.7

Target

System

TDOC

TMSC

TDIC

TCKC

GND

VDD

VREF

TDO

JTAG-

SMT2

GND

TMS

TDI

TCK

VIO

3.3V

VIO

200

The Adept SDK provides an example application that demonstrates how to communicate with a Class T4 TAP

controller using the MScan, OScan0, and OScan1 scan formats.

GPIO Pins

The JTAG-SMT2 has three general purpose IO pins (GPIO0, GPIO1, and GPIO2) that are useful for a variety of

different applications. Each pin features high speed, three-state input and output buffers. At power up, the JTAG-

SMT2 disables these output buffers and places the signals in a high-impedance state. Each signal remains in a

high-impedance state until a host application enables DPIO port 0 and configures the applicable pin as an output.

When the host application disables DPIO port 0, all GPIO pins revert to a high-impedance state. Weak pull-ups

(100K ohm) ensure that the GPIO signals do not float while not being actively driven (see Fig. 8).

IO Pin

(GPIO0, GPIO1, GPIO2)

1

0

0

K

VREF

OEGPIOx

Figure 6. Adding a current limiting resistor.

Figure 7. 200 Ohm resistor limiting current flow.

Figure 8. GPIO signals.