Linear burst address table (mode = gnd), Zz mode electrical characteristics – Cypress CY7C1338G User Manual

Page 5

CY7C1338G

Document #: 38-05521 Rev. *D

Page 5 of 17

Single Write Accesses Initiated by ADSP

This access is initiated when the following conditions are

satisfied at clock rise: (1) CE

1

, CE

2

, CE

3

are all asserted

active, and (2) ADSP is asserted LOW. The addresses

presented are loaded into the address register and the burst

inputs (GW, BWE, and BW[

A:D

])are ignored during this first

clock cycle. If the write inputs are asserted active (see Write

Cycle Descriptions table for appropriate states that indicate a

write) on the next clock rise, the appropriate data will be

latched and written into the device. Byte writes are allowed.

During byte writes, BW

A

controls DQ

A

and BWB controls DQ

B

.

BWC controls DQ

C

, and BW

D

controls DQ

D

. All I/Os are

tri-stated during a byte write.Since this is a common I/O

device, the asynchronous OE input signal must be deasserted

and the I/Os must be tri-stated prior to the presentation of data

to DQs. As a safety precaution, the data lines are tri-stated

once a write cycle is detected, regardless of the state of OE.

Single Write Accesses Initiated by ADSC

This write access is initiated when the following conditions are

satisfied at clock rise: (1) CE

1

, CE

2

, and CE

3

are all asserted

active, (2) ADSC is asserted LOW, (3) ADSP is deasserted

HIGH, and (4) the write input signals (GW, BWE, and BW

[A:D]

)

indicate a write access. ADSC is ignored if ADSP is active

LOW.

The addresses presented are loaded into the address register

and the burst counter/control logic and delivered to the

memory core. The information presented to DQ

[A:D]

will be

written into the specified address location. Byte writes are

allowed. During byte writes, BW

A

controls DQ

A

, BW

B

controls

DQ

B

, BW

C

controls DQ

C

, and BW

D

controls DQ

D

. All I/Os are

tri-stated when a write is detected, even a byte write. Since this

is a common I/O device, the asynchronous OE input signal

must be deasserted and the I/Os must be tri-stated prior to the

presentation of data to DQs. As a safety precaution, the data

lines are tri-stated once a write cycle is detected, regardless

of the state of OE.

Burst Sequences

The CY7C1338G provides an on-chip two-bit wraparound

burst counter inside the SRAM. The burst counter is fed by

A[1:0], and can follow either a linear or interleaved burst order.

The burst order is determined by the state of the MODE input.

A LOW on MODE will select a linear burst sequence. A HIGH

on MODE will select an interleaved burst order. Leaving

MODE unconnected will cause the device to default to a inter-

leaved burst sequence.

Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ

places the SRAM in a power conservation “sleep” mode. Two

clock cycles are required to enter into or exit from this “sleep”

mode. While in this mode, data integrity is guaranteed.

Accesses pending when entering the “sleep” mode are not

considered valid nor is the completion of the operation

guaranteed. The device must be deselected prior to entering

the “sleep” mode. CEs, ADSP, and ADSC must remain

inactive for the duration of t

ZZREC

after the ZZ input returns

LOW.

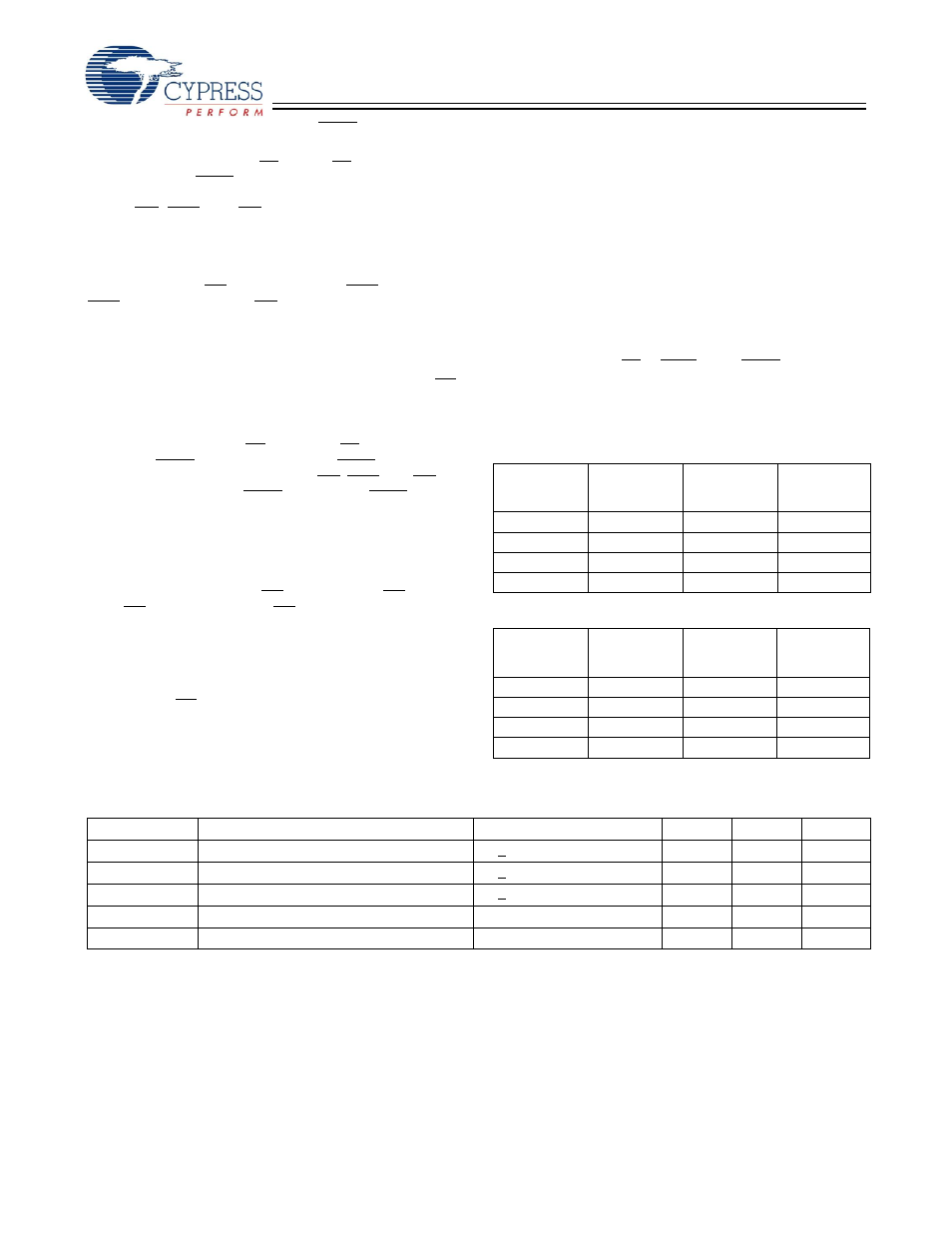

Interleaved Burst Address Table

(MODE = Floating or V

DD

)

First

Address

A1, A0

Second

Address

A1, A0

Third

Address

A1, A0

Fourth

Address

A1, A0

00

01

10

11

01

00

11

10

10

11

00

01

11

10

01

00

Linear Burst Address Table (MODE = GND)

First

Address

A

1

,

A

0

Second

Address

A

1

,

A

0

Third

Address

A

1

,

A

0

Fourth

Address

A

1

,

A

0

00

01

10

11

01

10

11

00

10

11

00

01

11

00

01

10

ZZ Mode Electrical Characteristics

Parameter

Description

Test Conditions

Min.

Max.

Unit

I

DDZZ

Sleep mode standby current

ZZ > V

DD

– 0.2V

40

mA

t

ZZS

Device operation to ZZ

ZZ > V

DD

– 0.2V

2t

CYC

ns

t

ZZREC

ZZ recovery time

ZZ < 0.2V

2t

CYC

ns

t

ZZI

ZZ active to sleep current

This parameter is sampled

2t

CYC

ns

t

RZZI

ZZ Inactive to exit sleep current

This parameter is sampled

0

ns