Document history page – Cypress CY7C1338G User Manual

Page 17

CY7C1338G

Document #: 38-05521 Rev. *D

Page 17 of 17

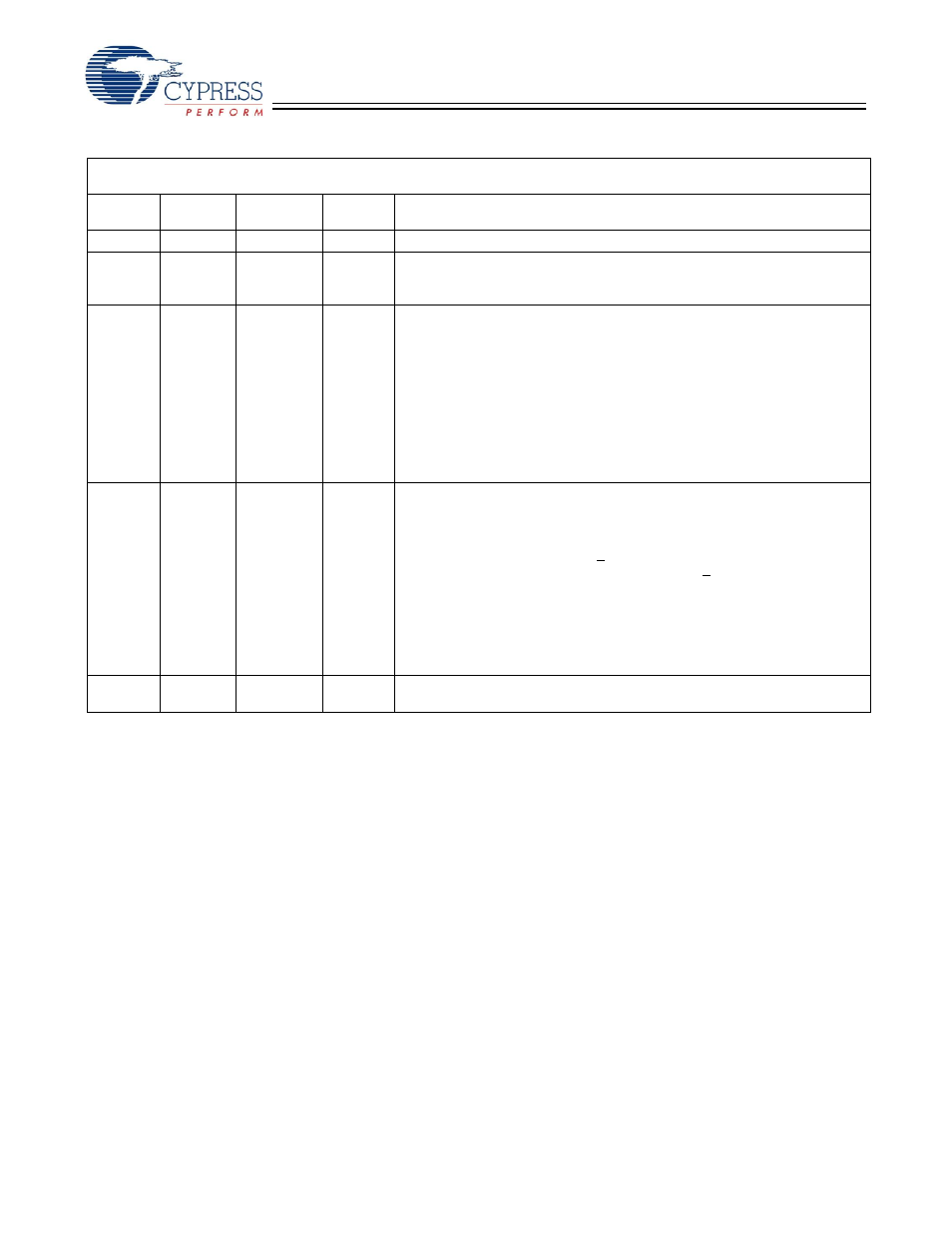

Document History Page

Document Title: CY7C1338G 4-Mbit (128K x 32) Flow-Through Sync SRAM

Document Number: 38-05521

REV.

ECN NO.

Issue Date

Orig. of

Change

Description of Change

**

224369

See ECN

RKF

New data sheet

*A

278513

See ECN

VBL

Deleted 66 MHz

Changed TQFP to PB-Free TQFP in Ordering Info section

Added PB-Free BG package

*B

333626

See ECN

SYT

Removed 117-MHz speed bin

Modified Address Expansion balls in the pinouts for 100 TQFP and 119 BGA

Packages as per JEDEC standards and updated the Pin Definitions accord-

ingly

Modified V

OL,

V

OH

test conditions

Replaced ‘Snooze’ with ‘Sleep’

Replaced TBD’s for

Θ

JA

and

Θ

JC

to their respective values on the Thermal

Resistance table

Removed comment on the availability of BG lead-free package

Updated the Ordering Information by shading and unshading MPNs as per

availability

*C

418633

See ECN

RXU

Converted from Preliminary to Final

Changed address of Cypress Semiconductor Corporation on Page# 1 from

“3901 North First Street” to “198 Champion Court”

Removed I

OS

from Electrical Characteristics table on Page #8

Modified test condition from V

IH

< V

DD

to

V

IH

< V

DD

Modified test condition from V

DDQ

< V

DD

to V

DDQ

< V

DD

Modified “Input Load” to “Input Leakage Current except ZZ and MODE” in the

Electrical Characteristics Table

Replaced Package Name column with Package Diagram in the Ordering

Information table

Replaced Package Diagram of 51-85050 from *A to *B

Updated the Ordering Information table

*D

480368

See ECN

VKN

Added the Maximum Rating for Supply Voltage on V

DDQ

Relative to GND.

Updated the Ordering Information table.