Clock constraints, Pipelining, Retiming – Achronix Synthesis User Manual

Page 9

UG018, April 15, 2013

9

Clock Constraints

It is a requirement for the user to define all clocks with a specific duty cycle and frequency or

clock period goal. The user can have multiple clocks with different clock frequencies. The

default frequency can be set for all clocks with the set_option -frequency Tcl command in the

Synplify project file. If the user does not specify a global frequency, the timing analyzer uses

a default. Achronix does not recommend using the default. Use the define_clock timing

constraint to override the default and specify unique clock frequency goals for each clock

signal. Additionally, the user can use the define_clock timing constraint to set the clock

frequency for a clock signal output from clock divider logic. The clock name is the output

signal name for the register instance. When constraining a differential clock the user only

needs to constrain the positive input.

Pipelining

When this switch is enabled in synthesis project file, the synthesis tool uses register balancing

and pipeline registers on multipliers and ROMs. Pipelining is the process of splitting logic

into stages so that the first stage can begin processing new inputs while the last stage is

finishing the previous inputs. This ensures better throughput and faster circuit performance.

If you are using selected technologies which use pipelining, you can also use the related

technique of retiming to improve performance. Same as enabling the Pipelining option on the

Options panel of the Implementation Options dialog box.

Retiming

When this switch is enabled the synthesis tool tries to improve the timing performance of

sequential circuits. The retiming process moves storage devices (flip-flops) across

computational elements with no memory (gates/LUTs) to improve the performance of the

circuit. This option also adds a retiming report to the log file. Same as enabling the Retiming

option on the Options panel of the Implementation Options dialog box. Use the

syn_allow_retiming attribute to enable or disable retiming for individual flip-flops.

Pipelining is automatically enabled when retiming is enabled.

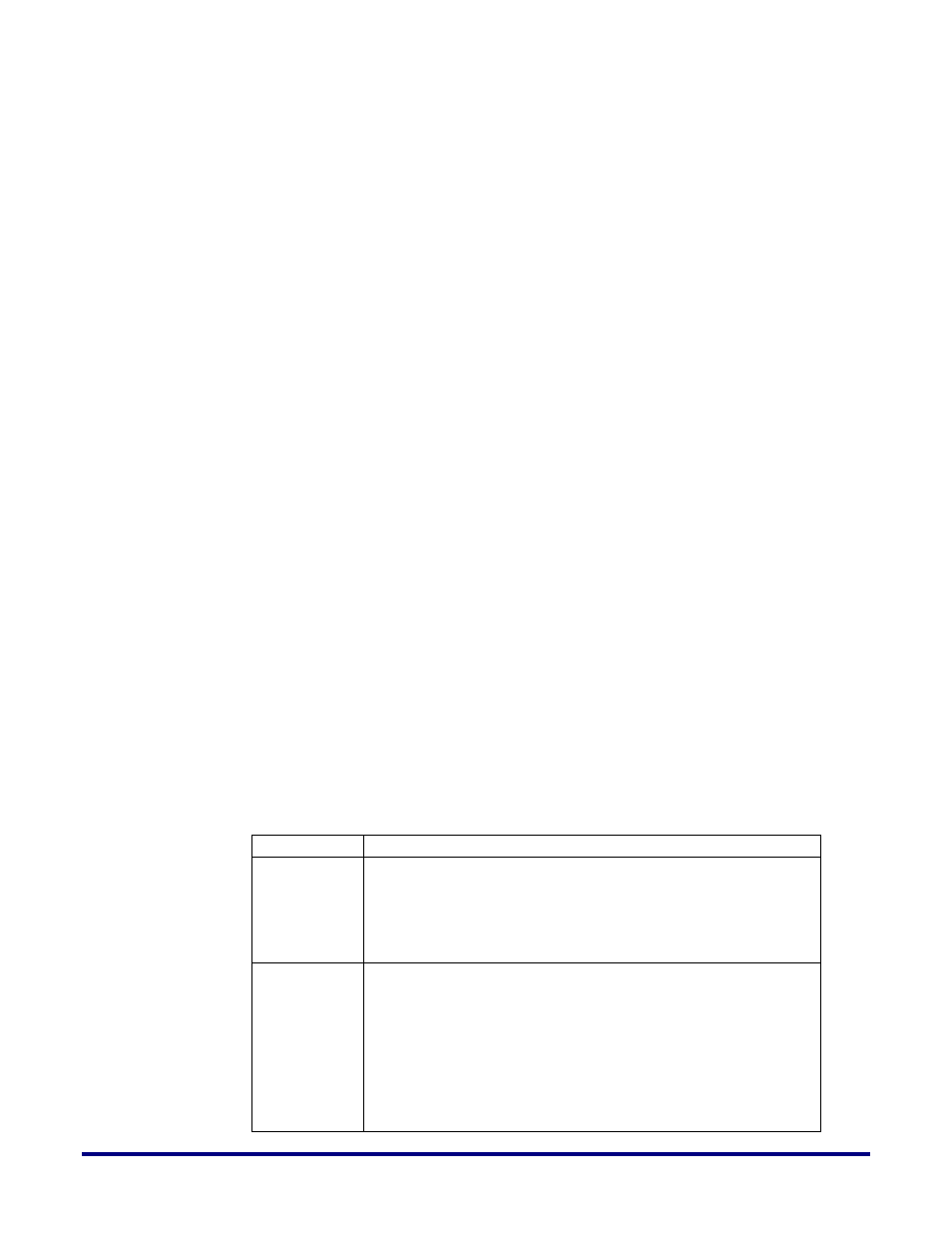

Syntax:

define_clock [ -disable ] [ -virtual] {clockObject} [ -freq MHz | -period ns ] [ -clockgroup domain ]

Option descriptions:

-disable

Disables a previous set clock constraint.

-virtual

Specifies arrival and required times on top level ports that are

enabled by clocks external to the chip (or block) that are being

synthesized. When specifying a name for a virtual clock, the

field can contain a unique name not associated with any port or

instance in the design.

{clockObject} This is a required parameter that specifies the name of the clock

object. Clocks can be defined on the following objects:

Top-level input ports (p:)

Nets (n:)

Instances (i:)

Output pins of instantiated cells (t:)

Clocks defined on any of the following objects WILL NOT be