Resource sharing, Verilog – Achronix Synthesis User Manual

Page 6

6

UG018, April 15, 2013

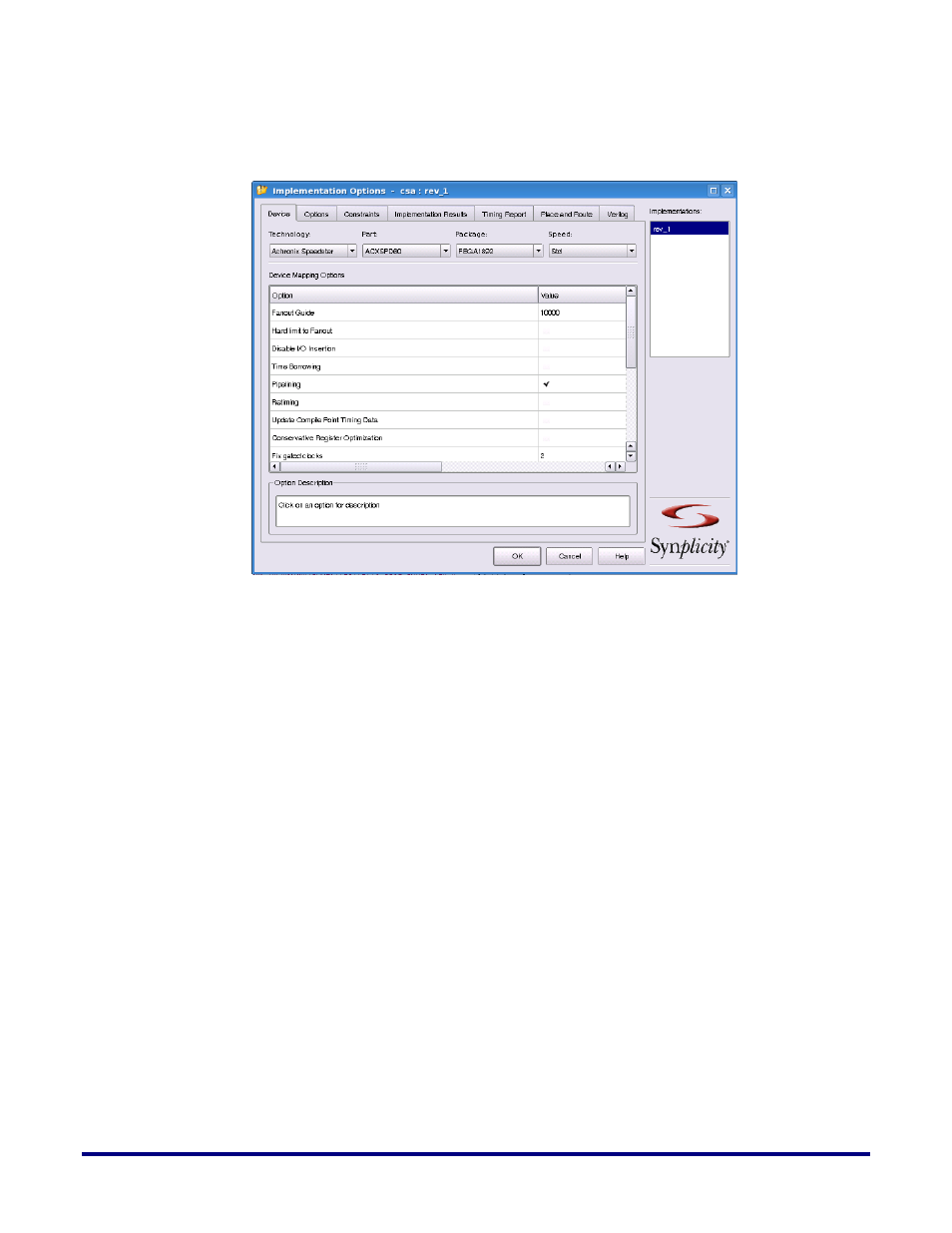

After adding the RTL files, the next step is to set the Implementation Options. By selecting

this option the following window will appear (Shown in Figure 6):

Figure 6 – Implementation Options

This dialog box shows the default options. For example the “Fanout Guide” defaults to

10,000, but you can modify this to any value. You can also check or uncheck the “Hard limit

to Fanout” option as well as the “Disable I/O Insertion” option.

If you do not want to infer IO buffers during synthesis, you will need to check the box under

the “Value” column. In the “Implementation Options” dialog box, “Device” is selected by

default. You can go through each tab and select the proper option according to your needs.

Here are some Achronix guidelines for these options.

Resource Sharing

Resource sharing can have a significant performance impact on loops and other critical

structures. Reviewing the synthesis results can identify resource sharing, for example

multiplexers in front of multipliers. Turning resource sharing off during synthesis can

improve performance.

Note: In some cases having resource sharing can actually improve performance. It is worth

experimenting as results are very design dependant

Verilog

Under this TAB section the user may define the Top-Level design module name. Achronix

also recommends selecting the Verilog 2001 from the Verilog Language box. The User can

also provide the parameter name of any parameter existing in the design along with a value

for the parameter. If you define the parameters in this manner, Synplify Pro will propagate

this value through the design. In this section the user can also add “Include Path Order” and