Cypress CY7C1380C User Manual

Cypress Hardware

18-Mb (512K x 36/1M x 18) Pipelined SRAM

CY7C1380C

CY7C1382C

Cypress Semiconductor Corporation

•

3901 North First Street

•

San Jose

,

CA 95134

•

408-943-2600

Document #: 38-05237 Rev. *D

Revised February 26, 2004

Features

• Supports bus operation up to 250 MHz

• Available speed grades are 250, 225, 200,166 and

133MHz

• Registered inputs and outputs for pipelined operation

• 3.3V core power supply

• 2.5V / 3.3V I/O operation

• Fast clock-to-output times

— 2.6 ns (for 250-MHz device)

— 2.8 ns (for 225-MHz device)

— 3.0 ns (for 200-MHz device)

— 3.4 ns (for 166-MHz device)

— 4.2 ns (for 133-MHz device)

• Provide high-performance 3-1-1-1 access rate

• User-selectable burst counter supporting Intel

®

Pentium interleaved or linear burst sequences

• Separate processor and controller address strobes

• Synchronous self-timed writes

• Asynchronous output enable

• Single Cycle Chip Deselect

• Offered in JEDEC-standard 100-pin TQFP, 119-ball BGA

and 165-Ball fBGA packages

• IEEE 1149.1 JTAG-Compatible Boundary Scan

• “ZZ” Sleep Mode Option

Functional Description

[1]

The CY7C1380C/CY7C1382C SRAM integrates 524,288 x 36

and 1,048,576 x 18 SRAM cells with advanced synchronous

peripheral circuitry and a two-bit counter for internal burst

operation. All synchronous inputs are gated by registers

controlled by a positive-edge-triggered Clock Input (CLK). The

synchronous inputs include all addresses, all data inputs,

address-pipelining Chip Enable (CE

1

), depth-expansion Chip

Enables (CE

2

and

CE

3

[2]

), Burst Control inputs (ADSC, ADSP,

and ADV), Write Enables (BW

X

, and BWE), and Global Write

(GW). Asynchronous inputs include the Output Enable (OE)

and the ZZ pin.

Addresses and chip enables are registered at rising edge of

clock when either Address Strobe Processor (ADSP) or

Address Strobe Controller (ADSC) are active. Subsequent

burst addresses can be internally generated as controlled by

the Advance pin (ADV).

Address, data inputs, and write controls are registered on-chip

to initiate a self-timed Write cycle.This part supports Byte Write

operations (see Pin Descriptions and Truth Table for further

details). Write cycles can be one to two or four bytes wide as

controlled by the byte write control inputs. GW when active

LOW causes all bytes to be written.

The CY7C1380C/CY7C1382C operates from a +3.3V core

power supply while all outputs may operate with either a +2.5

or +3.3V supply. All inputs and outputs are JEDEC-standard

JESD8-5-compatible.

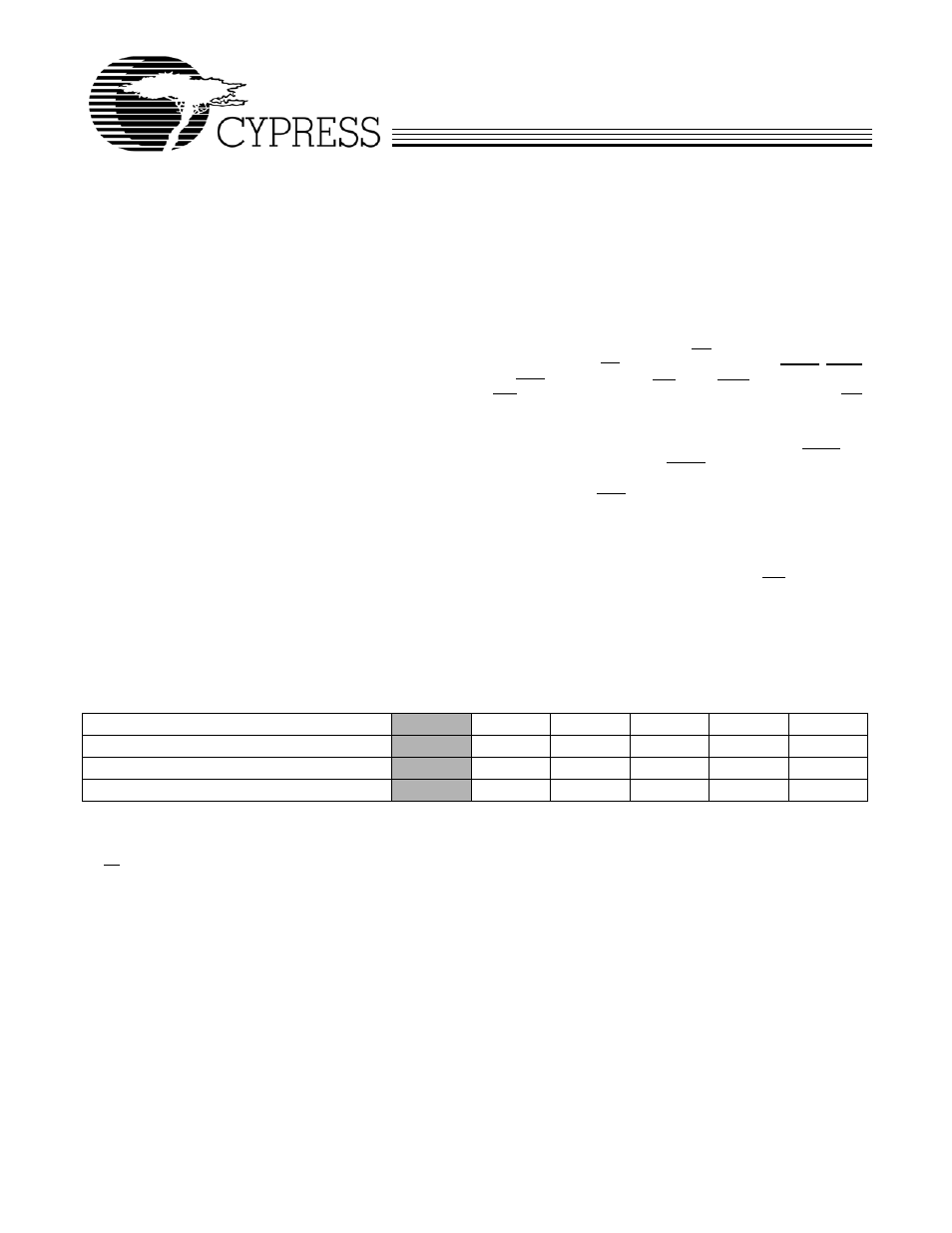

Selection Guide

250 MHz

225 MHz

200 MHz

167 MHz

133 MHz

Unit

Maximum Access Time

2.6

2.8

3.0

3.4

4.2

ns

Maximum Operating Current

350

325

300

275

245

mA

Maximum CMOS Standby Current

70

70

70

70

70

mA

Shaded areas contain advance information.

Please contact your local Cypress sales representative for availability of these parts.

Notes:

1. For best–practices recommendations, please refer to the Cypress application note System Design Guidelines on www.cypress.com.

2. CE

3

, CE

2

are for TQFP and 165 fBGA package only. 119 BGA is offered only in 1 Chip Enable.