Cypress CY7C1360C User Manual

Page 15

CY7C1360C

CY7C1362C

Document #: 38-05540 Rev. *H

Page 15 of 31

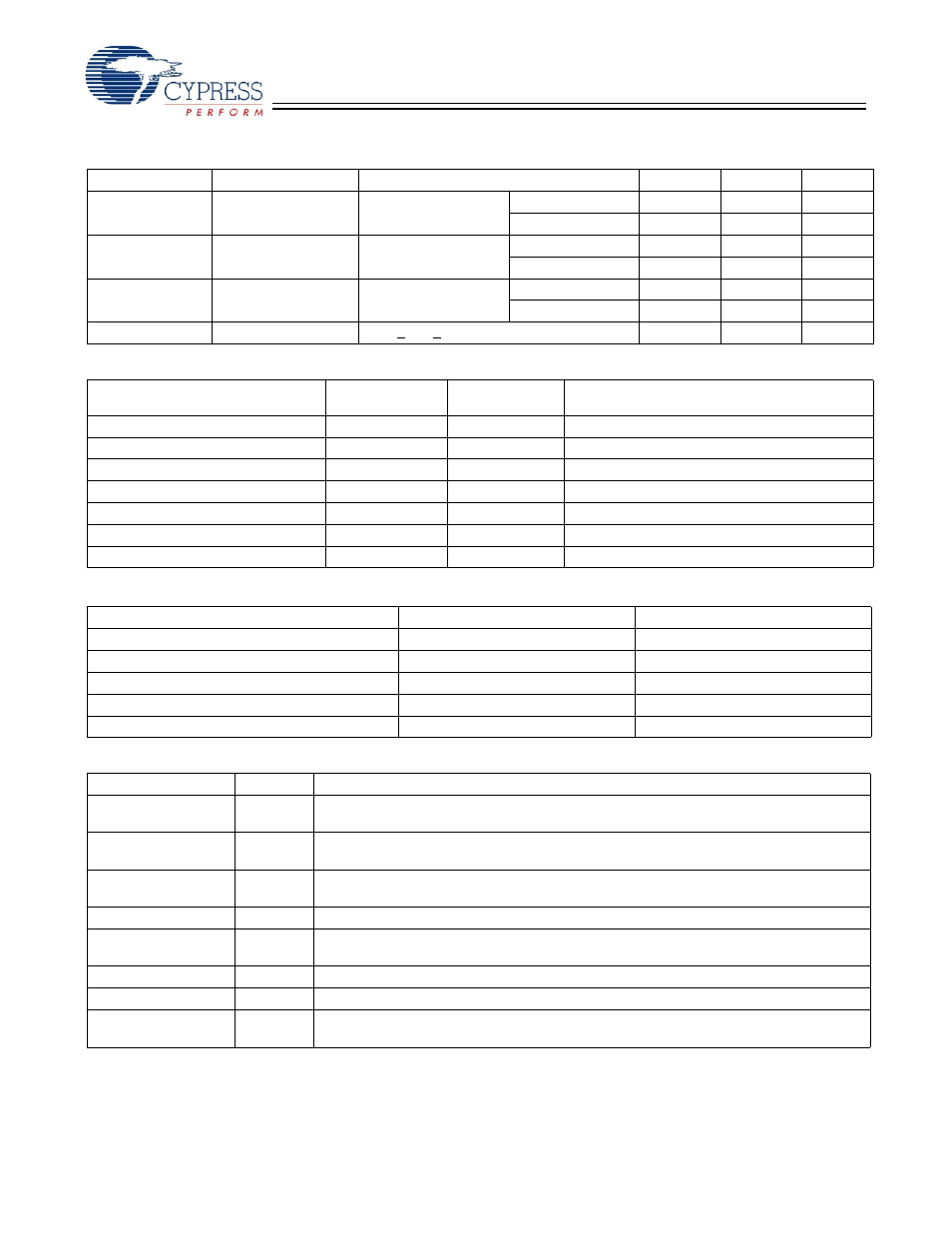

V

OL2

Output LOW Voltage

I

OL

= 100 µA

V

DDQ

= 3.3V

0.2

V

V

DDQ

= 2.5V

0.2

V

V

IH

Input HIGH Voltage

V

DDQ

= 3.3V

2.0

V

DD

+ 0.3

V

V

DDQ

= 2.5V

1.7

V

DD

+ 0.3

V

V

IL

Input LOW Voltage

V

DDQ

= 3.3V

–0.5

0.7

V

V

DDQ

= 2.5V

–0.3

0.7

V

I

X

Input Load Current

GND < V

IN

< V

DDQ

–5

5

µA

Identification Register Definitions

Instruction Field

CY7C1360C

(256KX36)

CY7C1362C

(512KX18)

Description

Revision Number (31:29)

000

000

Describes the version number

Device Depth (28:24)

[13]

01011

01011

Reserved for Internal Use

Device Width (23:18) 119-BGA

101000

101000

Defines memory type and architecture

Device Width (23:18) 165- FBGA

000000

000000

Defines memory type and architecture

Cypress Device ID (17:12)

100110

010110

Defines width and density

Cypress JEDEC ID Code (11:1)

00000110100

00000110100

Allows unique identification of SRAM vendor

ID Register Presence Indicator (0)

1

1

Indicates the presence of an ID register

TAP DC Electrical Characteristics And Operating Conditions

(0°C < T

A

< +70°C; V

DD

= 3.3V ±0.165V unless otherwise noted)

[12]

(continued)

Parameter

Description

Conditions

Min.

Max.

Unit

Scan Register Sizes

Register Name

Bit Size (x36)

Bit Size (x18)

Instruction

3

3

Bypass

1

1

ID

32

32

Boundary Scan Order (119-ball BGA package)

71

71

Boundary Scan Order (165-ball FBGA package)

71

71

Identification Codes

Instruction

Code

Description

EXTEST

000

Captures I/O ring contents. Places the boundary scan register between TDI and TDO.

Forces all SRAM outputs to High-Z state.

IDCODE

001

Loads the ID register with the vendor ID code and places the register between TDI and

TDO. This operation does not affect SRAM operations.

SAMPLE Z

010

Captures I/O ring contents. Places the boundary scan register between TDI and TDO.

Forces all SRAM output drivers to a High-Z state.

RESERVED

011

Do Not Use: This instruction is reserved for future use.

SAMPLE/PRELOAD

100

Captures I/O ring contents. Places the boundary scan register between TDI and TDO.

Does not affect SRAM operation.

RESERVED

101

Do Not Use: This instruction is reserved for future use.

RESERVED

110

Do Not Use: This instruction is reserved for future use.

BYPASS

111

Places the bypass register between TDI and TDO. This operation does not affect SRAM

operations.

Note:

13. Bit #24 is “1” in the Register Definitions for both 2.5V and 3.3V versions of this device.