Tap controller block diagram – Cypress CY7C1360C User Manual

Page 12

CY7C1360C

CY7C1362C

Document #: 38-05540 Rev. *H

Page 12 of 31

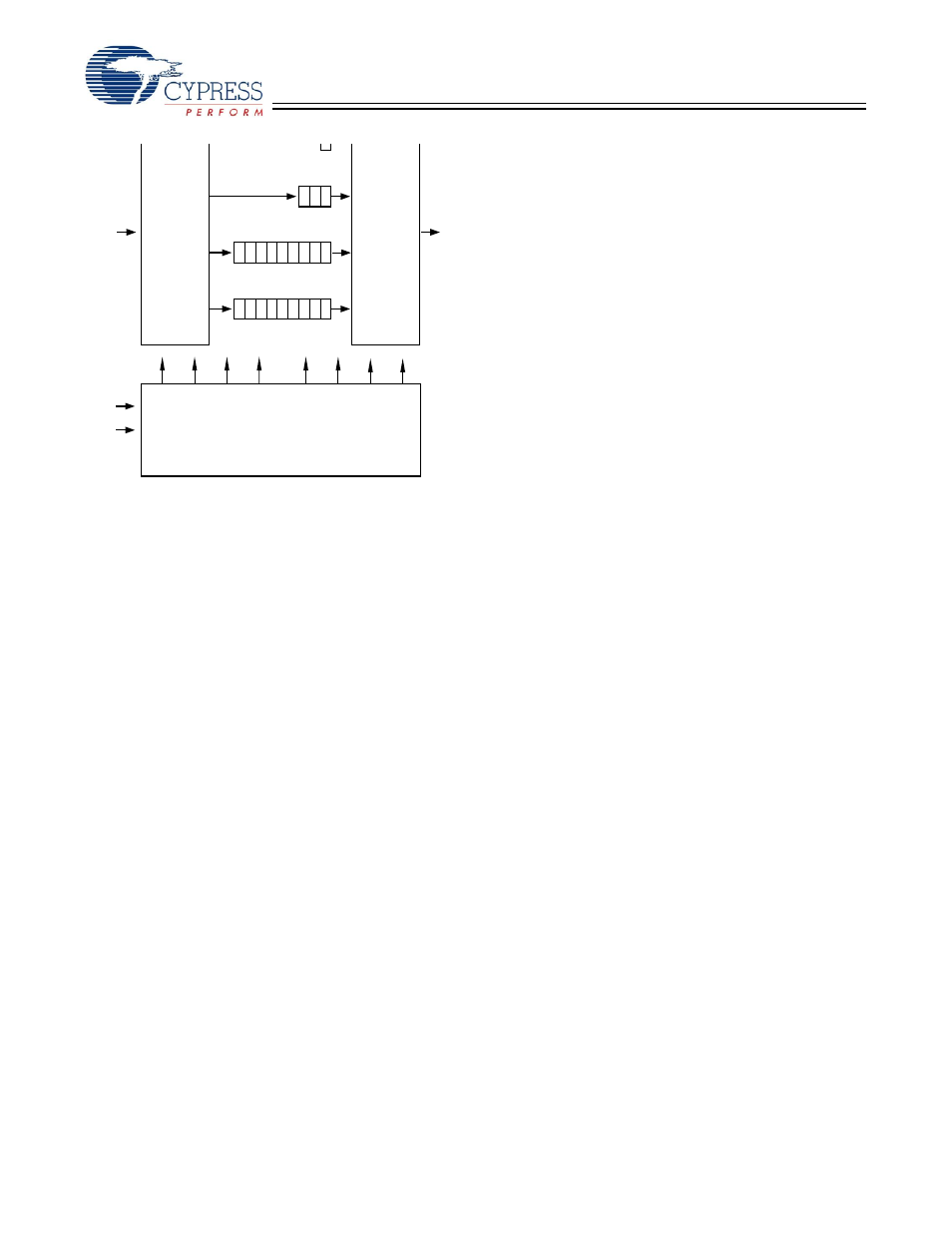

TAP Controller Block Diagram

Performing a TAP Reset

A RESET is performed by forcing TMS HIGH (V

DD

) for five

rising edges of TCK. This RESET does not affect the operation

of the SRAM and may be performed while the SRAM is

operating.

At power-up, the TAP is reset internally to ensure that TDO

comes up in a High-Z state.

TAP Registers

Registers are connected between the TDI and TDO balls and

allow data to be scanned into and out of the SRAM test

circuitry. Only one register can be selected at a time through

the instruction register. Data is serially loaded into the TDI ball

on the rising edge of TCK. Data is output on the TDO ball on

the falling edge of TCK.

Instruction Register

Three-bit instructions can be serially loaded into the instruction

register. This register is loaded when it is placed between the

TDI and TDO balls as shown in the Tap Controller Block

Diagram. Upon power-up, the instruction register is loaded

with the IDCODE instruction. It is also loaded with the IDCODE

instruction if the controller is placed in a reset state as

described in the previous section.

When the TAP controller is in the Capture-IR state, the two

least significant bits are loaded with a binary “01” pattern to

allow for fault isolation of the board-level serial test data path.

Bypass Register

To save time when serially shifting data through registers, it is

sometimes advantageous to skip certain chips. The bypass

register is a single-bit register that can be placed between the

TDI and TDO balls. This allows data to be shifted through the

SRAM with minimal delay. The bypass register is set LOW

(V

SS

) when the BYPASS instruction is executed.

Boundary Scan Register

The boundary scan register is connected to all the input and

bidirectional balls on the SRAM.

The boundary scan register is loaded with the contents of the

RAM I/O ring when the TAP controller is in the Capture-DR

state and is then placed between the TDI and TDO balls when

the controller is moved to the Shift-DR state. The EXTEST,

SAMPLE/PRELOAD and SAMPLE Z instructions can be used

to capture the contents of the I/O ring.

The Boundary Scan Order tables show the order in which the

bits are connected. Each bit corresponds to one of the bumps

on the SRAM package. The MSB of the register is connected

to TDI and the LSB is connected to TDO.

Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code

during the Capture-DR state when the IDCODE command is

loaded in the instruction register. The IDCODE is hardwired

into the SRAM and can be shifted out when the TAP controller

is in the Shift-DR state. The ID register has a vendor code and

other information described in the Identification Register

Definitions table.

TAP Instruction Set

Overview

Eight different instructions are possible with the three-bit

instruction register. All combinations are listed in the

Instruction Codes table. Three of these instructions are listed

as RESERVED and should not be used. The other five instruc-

tions are described in detail below.

The TAP controller used in this SRAM is not fully compliant to

the 1149.1 convention because some of the mandatory 1149.1

instructions are not fully implemented.

The TAP controller cannot be used to load address data or

control signals into the SRAM and cannot preload the I/O

buffers. The SRAM does not implement the 1149.1 commands

EXTEST or INTEST or the PRELOAD portion of

SAMPLE/PRELOAD; rather, it performs a capture of the I/O

ring when these instructions are executed.

Instructions are loaded into the TAP controller during the

Shift-IR state when the instruction register is placed between

TDI and TDO. During this state, instructions are shifted

through the instruction register through the TDI and TDO balls.

To execute the instruction once it is shifted in, the TAP

controller needs to be moved into the Update-IR state.

EXTEST

EXTEST is a mandatory 1149.1 instruction which is to be

executed whenever the instruction register is loaded with all

0s. EXTEST is not implemented in this SRAM TAP controller,

and therefore this device is not compliant to 1149.1. The TAP

controller does recognize an all-0 instruction.

When an EXTEST instruction is loaded into the instruction

register, the SRAM responds as if a SAMPLE/PRELOAD

instruction has been loaded. There is one difference between

the two instructions. Unlike the SAMPLE/PRELOAD

instruction, EXTEST places the SRAM outputs in a High-Z

state.

Bypass Register

0

Instruction Register

0

1

2

Identification Register

0

1

2

29

30

31

.

.

.

Boundary Scan Register

0

1

2

.

.

x

.

.

.

S

election

Circuitr

y

Selection

Circuitry

TCK

TMS

TAP CONTROLLER

TDI

TDO