Output sequencing – Vicor PFC MegaPAC-HPEL Power Factor Corrected AC-DC Switchers User Manual

Page 28

UG:119

vicorpower.com

Applications Engineering: 800 927.9474

Page 28

Output Sequencing

Using the MegaPAC's standard Input Interface Connector (J10) along with the

ConverterPAC's optional DC OK Option, it is possible to implement unique output

voltage power up and power down sequences. Below is an example showing how this

may be done.

Requirement: 5 V must start before the 3.3 V output. If the 5 V output is lost, the 3.3 V

output must turn off.

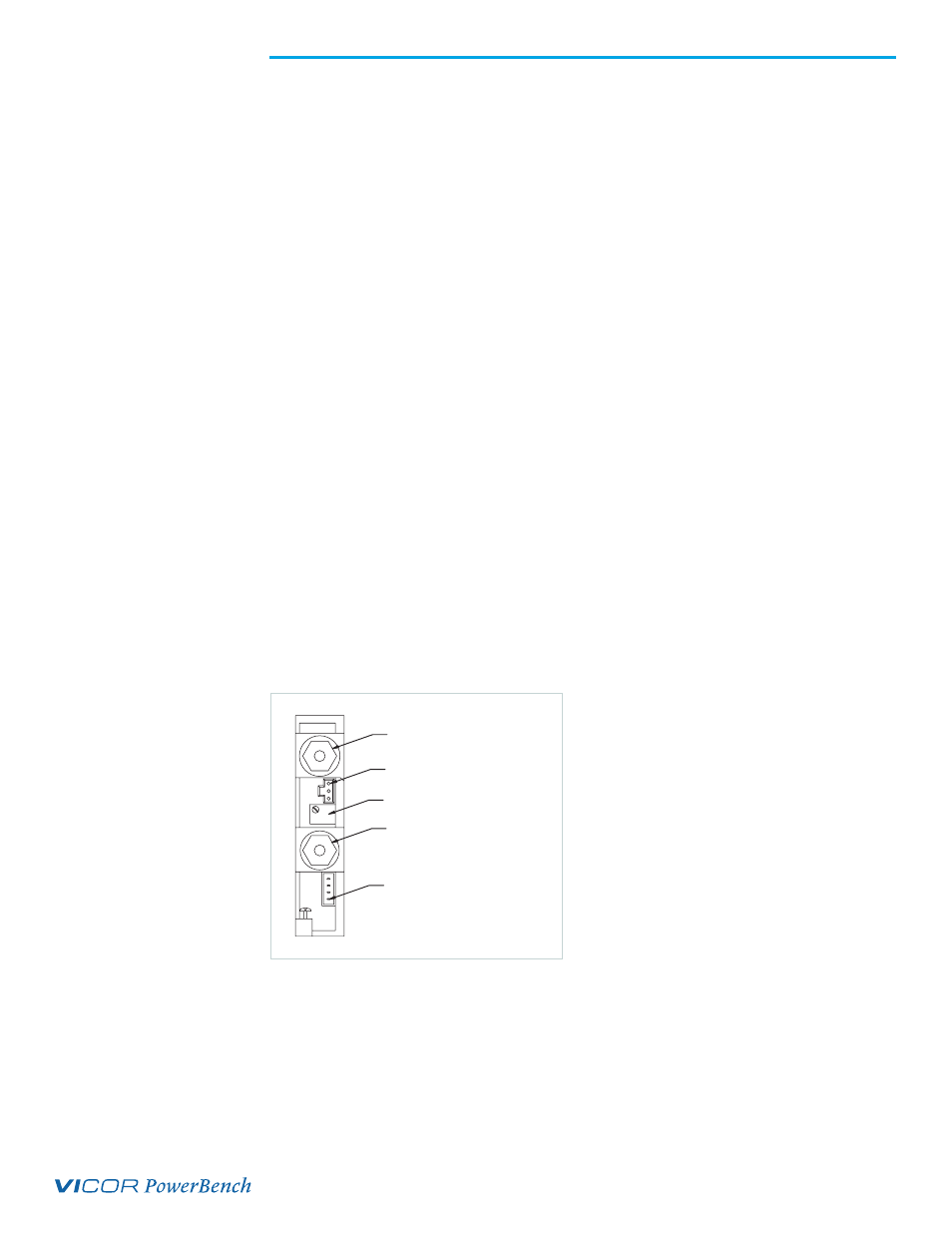

The first step in meeting this requirement is to configure the 5 V QPAC with the DC OK

Option, which is indicated by a "D" designator in the QPAC's part number, located on

the top surface of each QPAC above the +Vout. Any QPAC that has the DC OK option

will also have the 4 Pin J3 DC OK connector installed. To order a QPAC with the DC OK

option, please contact Vicor's customer service department for assistance. The DC OK

option monitors the output voltage of a given ConverterPAC and provides a TTL logic

signal depending on its output voltage.

Figure 17 shows the correct wiring connections between the Power Good Connector (J3)

of a 5 V QPAC and the Input Interface Connector (J10) of a typical

PFC MegaPAC-EL configuration. In this example, the 3.3 V QPAC is located in the slot #7

and the 5 V QPAC (with the DC OK option) is located in slot #8. In order for the Power

Good option to properly function, it requires a 5 V source to provide the necessary Vcc

pull up. This 5 V source is conveniently available using the +5 V aux source from the

Input Interface Connector (J10-9 and J10-10). With a Vcc voltage properly applied to the

5 V QPAC's Power Good Connector (J3-1 and J3-4), the Power Good signal (J3-3) can

now be connected to the Enable/Disable control pin for slot #7 (J10-7). The 5 V QPAC's

Power Good signal will remain low until its output has reached approximately 95% of

its nominal output voltage. This will keep the 3.3 V output in disabled mode, allowing

the 5 V output to reach regulation first. In addition, should the 5 V output drop below

85% the Power Good signal will drop low and disable the 3.3 V output. Figures 18 and 19

show the startup and shutdown waveforms for the circuit shown in Figure 17.

Figure 15.

QPAC Pinout

J2 Pin 1

J3 pin 1 (DC OK Option)

+ Vout

- Vout

Vtrim Pot Adjust (Option)