3 test method – Anritsu MP1763C User Manual

Page 68

6-2

Section 6 PERFORMANCE TEST

6.3 Test Method

Connect the MP1763C DATA and CLOCK1 connectors to the error detector as shown in 6.2-(1).

Set Error Free at the setting shown below.

Pattern

LOGIC

POS

PRBS

2

31

-1

Mark ratio

1/2

Output

DATA

amplitude

0.5 Vp-p

offset

0 Vp-p

CLOCK

amplitude

0.5 Vp-p

offset

0.0 V

OH

Delay

0 ps

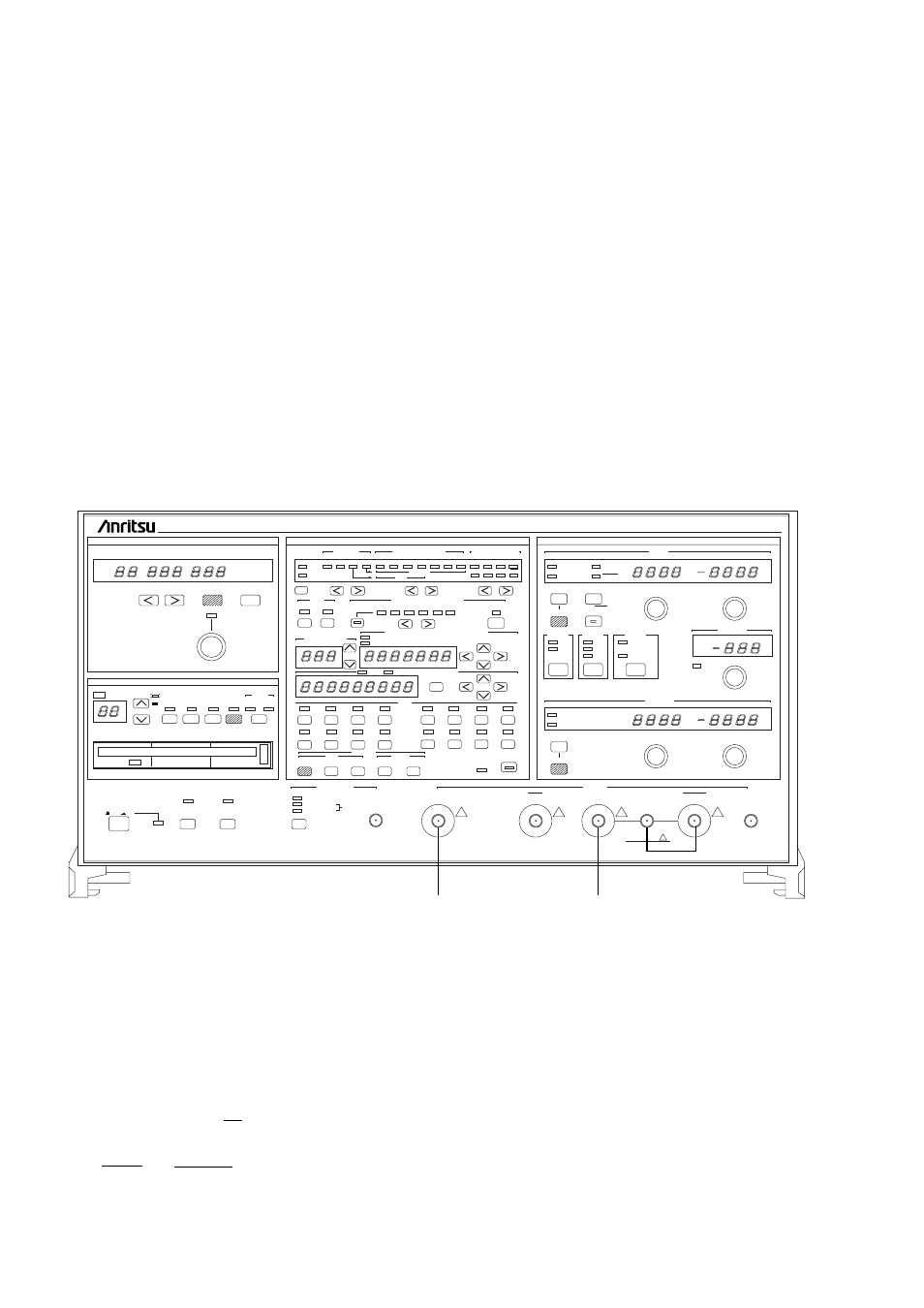

Fig. 6.3-1 Connection of front panel

Set the Error Detector to the same conditions as the MP1763C or set the margin to maximum. Confirm that the following

points are Error Free:

Frequency

50 MHz, 1 GHz, 3 GHz, 5 GHz, 12.5 GHz

Amplitude

0.25 Vp-p, 2.0 Vp-p

Offset

0V

OH

, -V

OH

, +2 V

OH

Mark ratio

1/2, 1/8, 1/2, 7/8

Check DATA and CLOCK1 in the same way. However, since CLOCK is inverted, invert the detector CLOCK polarity.

SINGLE

DISPLAY

PULSE PATTERN GENERATOR MP1763C 0.05 - 12.5GHz

INTERNAL CLOCK (OPTION.01)

PATTERN

MEMORY

TUNING RESOLUTION

FREQUENCY

MHz

kMz

OUTPUT

EXIST

DIR

FILE No.

RECALL

DELETE

SAVE

RESAVE

SHIFT

PATT OTHERS

MODE

LOGIC

PATTERN

PRBS / ZERO SUBST

PRBS MARK RATIO

2 - 1

2

POS

NEG

ALTNDATA Z.S PRBS 7 9 11 15 20 23 31 0/8 1/8 1/4 1/2

8/8 7/8 3/4 1/2

ALTN

ERROR ADDITION(1

10 )

- N

A

B

ON

4 5 6 7 8 9

DATA LENGTH/ZERO SUBST LENGTH

DATA LENGTH

ZERO SUBST LENGTH

A / B LOOP TIME

PAGE/ PATTERN SYNC POSITION

BIT

1 2 3 4

5 6 7 8

9 10 11 12

13 14 15 16

ALL

PAGE

PRESET

PATTERN

LOADING

TRACKING

GUARD 0 1

0 1

ps

DELAY TIME

BUSY

CLOCK 1

50

GND

ECL

AMPLITUDE

Vp - p

OFFSET

V

ECL

GUARD

ECL

DISPLAY

DATA/DATA

TRACKING

GUARD

OUTPUT

ON

OFF

OFFSET

V

OH

V

TH

V

OL

DISPLAY

1/1 SPEED

1/4 SPEED

(OPTION.03)

OUTPUT

DATA DATA CLOCK 1 DUMMY CLOCK 1 CLOCK 2

50

50

50

CAUTION

CONNECT THE UNUSE

OUTPUT TO THE DUMMY

50

0 / - 1V 50

1 / 64 CLOCK

FIXED POSN

VAR POSN

PATTERN

SYNC

PANEL

LOCK

GPIB

REMOTE

LOCAL

POWER

OFF ON

SYNC OUTPUT

0 / - 1V 50

DATA

50

GND

ECL

DATA

DATA

AMPLITUDE

Vp - p

OFFSET

V

CLOCK 1