Cs8900a – Cirrus Logic CS8900A User Manual

Page 46

46

DS271F5

CS8900A

Crystal LAN™ Ethernet Controller

CIRRUS LOGIC PRODUCT DATASHEET

Reset value is: 0000 0000 0000 0000

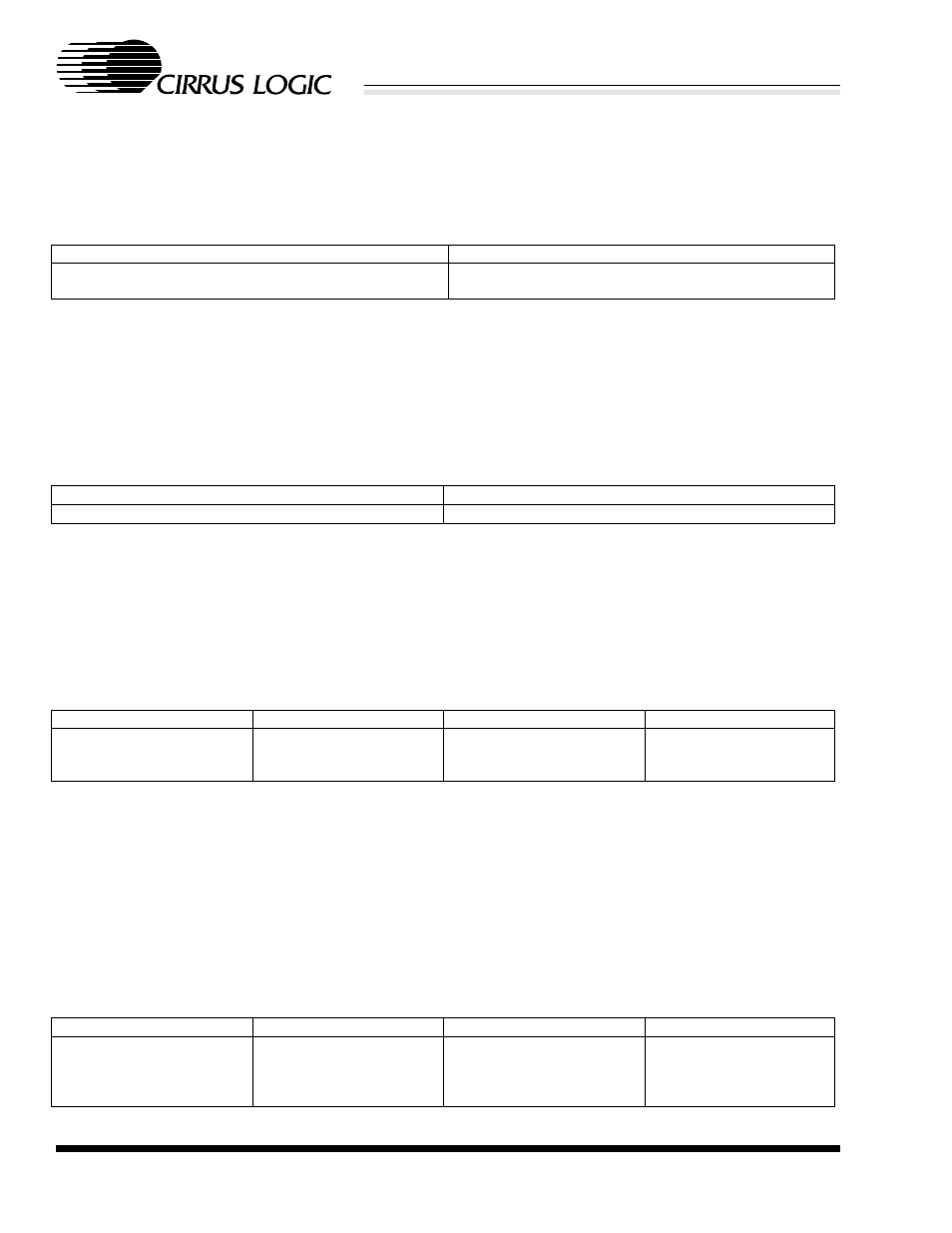

4.3.6 DMA Frame Count

(Read only, Address: PacketPage base + 0028h)

The lower 12 bits of the DMA Frame Count register define the number of valid frames transferred via DMA since the

last readout of this register. The upper 4 bits are reserved. See Section 5.3 on page 90.

Reset value is: XXXX 0000 0000 0000

4.3.7 RxDMA Byte Count

(Read only, Address: PacketPage base + 002Ah)

The RxDMA Byte Count register describes the valid number of bytes DMAed since the last readout. See Section 5.3

on page 90.

Reset value is: 0000 0000 0000 0000

4.3.8 Memory Base Address

(Read/Write, Address: PacketPage base + 002Ch)

Memory Base Address: The lower three bytes (002Ch, 002Dh, and 002Eh) are used for the 20-bit memory base

address. The upper three nibbles are reserved.

After reset, if no EEPROM is found by the CS8900A, then the register has the following initial state. If an EEPROM

is found, then the register's initial value may be set by the EEPROM. See Section 3.3 on page 19.

Reset value is: XXXX XXXX XXXX 0000 0000 0000 0000 0000

4.3.9 Boot PROM Base Address

(Read/Write, Address: PacketPage base + 0030h)

Address 0029h

Address 0028h

Most significant byte of frame count

(most-significant nibble always 0h)

Least significant byte of frame count

Address 002Bh

Address 002Ah

Most significant byte of byte count

Least significant byte of byte count

Address 002Fh

Address 002Eh

Address 002Dh

Address 002Ch

Reserved

The most significant nibble of

memory base address. The

high-order nibble is reserved.

Contains portion of memory

base address.

The least significant byte of

the memory base address.

Address 0033h

Address 0032h

Address 0031h

Address 0030h

Reserved

The most significant nibble of

Boot PROM base address.

The high-order nibble is

reserved.

Contains portion of Boot PROM

base address.

The least significant byte of

the Boot PROM base

address.