1 integrated memory, 2 bus interface registers, 3 status and control registers – Cirrus Logic CS8900A User Manual

Page 41: 4 initiate transmit registers, 5 address filter registers, 6 receive and transmit frame locations, Cs8900a

DS271F5

41

CS8900A

Crystal LAN™ Ethernet Controller

CIRRUS LOGIC PRODUCT DATASHEET

4.0 PACKETPAGE ARCHITECTURE

4.1 PacketPage Overview

The CS8900A architecture is based on a

unique, highly-efficient method of accessing

internal registers and buffer memory known as

PacketPage. PacketPage provides a unified

way of controlling the CS8900A in Memory or

I/O space that minimizes CPU overhead and

simplifies software. It provides a flexible set of

performance features and configuration op-

tions, allowing designers to develop Ethernet

circuits that meet their particular system re-

quirements.

4.1.1 Integrated Memory

Central to the CS8900A architecture is a 4-

Kbyte page of integrated RAM known as Pack-

etPage memory. PacketPage memory is used

for temporary storage of transmit and receive

frames, and for internal registers. Access to

this memory is done directly, through Memory

space operations (Section 4.9 on page 73), or

indirectly, through I/O space operations

(Section 4.10 on page 75). In most cases,

Memory Mode will provide the best overall per-

formance, because ISA Memory operations

require fewer cycles than I/O operations. I/O

Mode is the CS8900A’s default configuration

and is used when memory space is not avail-

able or when special operations are required

(e.g. waking the CS8900A from the Software

Suspend State requires the host to write to the

CS8900A’s assigned I/O space).

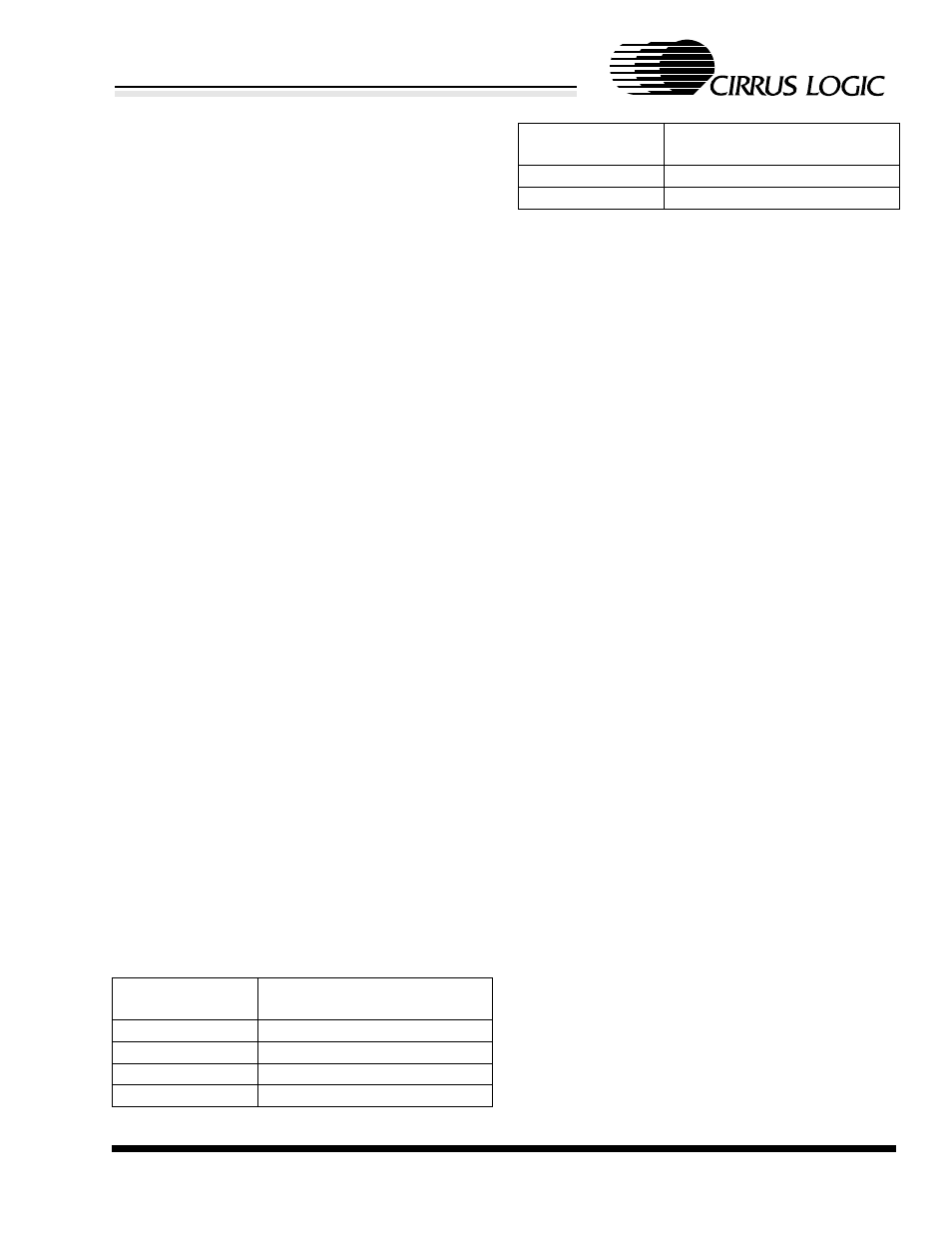

The user-accessible portion of PacketPage

memory is organized into the following six sec-

tions:

4.1.2 Bus Interface Registers

The Bus Interface registers are used to config-

ure the CS8900A’s ISA-bus interface and to

map the CS8900A into the host system’s I/O

and Memory space. Most of these registers

are written only during initialization, remaining

unchanged while the CS8900A is in normal

operating mode. The exceptions to this are the

DMA registers which are modified continually

whenever the CS8900A is using DMA. These

registers are described in more detail in

Section 4.3 on page 44.

4.1.3 Status and Control Registers

The Status and Control registers are the pri-

mary means of controlling and getting status of

the CS8900A. They are described in more de-

tail in Section 4.4 on page 49.

4.1.4 Initiate Transmit Registers

The TxCMD/TxLength registers are used to

initiate Ethernet frame transmission. These

registers are described in more detail in

Section 4.5 on page 69. (See Section 5.6 on

page 99 for a description of frame transmis-

sion.)

4.1.5 Address Filter Registers

The Filter registers store the Individual Ad-

dress filter and Logical Address filter used by

the Destination Address (DA) filter. These reg-

isters are described in more detail in

Section 4.6 on page 71. For a description of

the DA filter, see Section 5.2.10 on page 87.

4.1.6 Receive and Transmit Frame Loca-

tions

The Receive and Transmit Frame PacketPage

locations are used to transfer Ethernet frames

PacketPage

Address

Contents

0000h - 0045h

Bus Interface Registers

0100h - 013Fh

Status and Control Registers

0140h - 014Fh

Initiate Transmit Registers

0150h - 015Dh

Address Filter Registers

0400h

Receive Frame Location

0A00h

Transmit Frame Location

PacketPage

Address

Contents