Cs8130, Register 15, status register, Register 12, output pin control register – Cirrus Logic CS8130 User Manual

Page 18: Register 13, control register #3

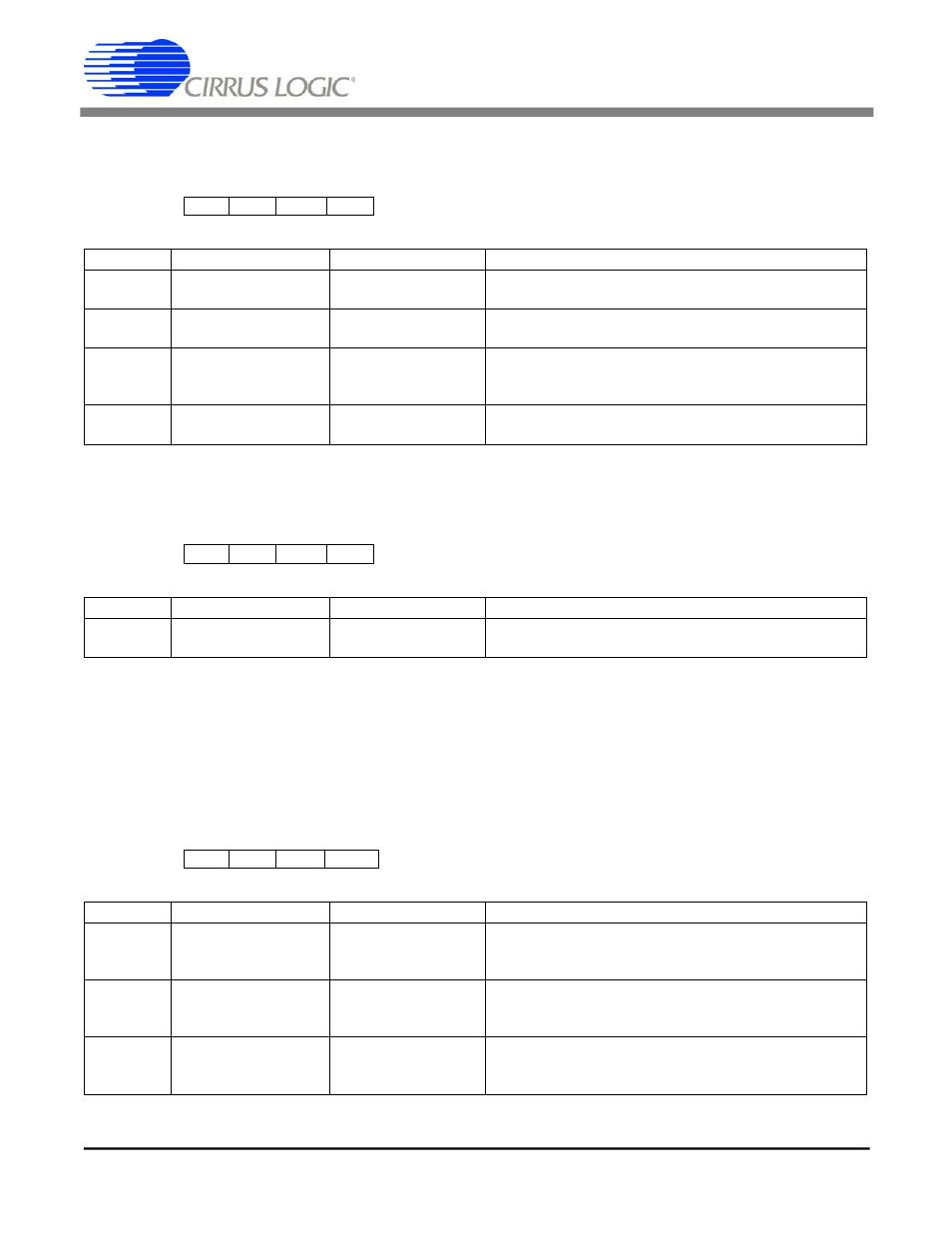

Register 15, Status Register

D3

D2

D1

D0

0

OSCR

ERR

DMOD

0

0

0

Register

Reset (R)

BIT

NAME

VALUE

FUNCTION

OSCR

Oscillator running

flag

0

1

Oscillator not running, using external clock input,

oscillator circuit is powered down.

Oscillator running, EXTCLK is an output, if enabled.

ERR

Framing error flag

0

1

R No error

A framing error has occurred since the last read of

this bit. Resets after read

DMOD

Detected

Modulation Type

0

1

R IrDA pulse style data format detected

Amplitude modulated carrier style data format

detected

To read this register, write 0000 to address 15. Independent of the setting of the ECHO bit, the CS8130

will transmit the above contents, with an address field of 1111.

Register 12, Output Pin Control Register

D3

D2

D1

D0

RXDT

RXDH

FORT

FORH

0

1

0

1

Register

Reset (R)

BIT

NAME

VALUE

FUNCTION

RXDT

RXD output pin

three-state enable

0

1

R In power down, RXD will go high or low.

In power down, RXD will float.

RXDH

RXD output pin

high/low enable

0

1

R

In power down, RXD will go low, if RXDT = 0

In power down, RXD will go high, if RXDT = 0

FORT

FORM/BSY output

pin three-state

enable

0

1

R In power down, FORM/BSY will go high or low.

In power down, FORM/BSY will float.

FORH

FORM/BSY output

pin high/low enable

0

1

R

In power down, FORM/BSY will go low, if FORT = 0

In power down, FORM/BSY will go high, if FORT = 0

Register 13, Control Register #3

D3

D2

D1

D0

0

0

0

SHDW

0

0

0

0

Register

Reset (R)

BIT

NAME

VALUE

FUNCTION

SHDW

Shadow register set

enable

0

1

R Enable access to registers 0 though 15

Enable access to shadow registers (16 through 31)

CS8130

18

DS134PP2

CS8130

18

DS134F1