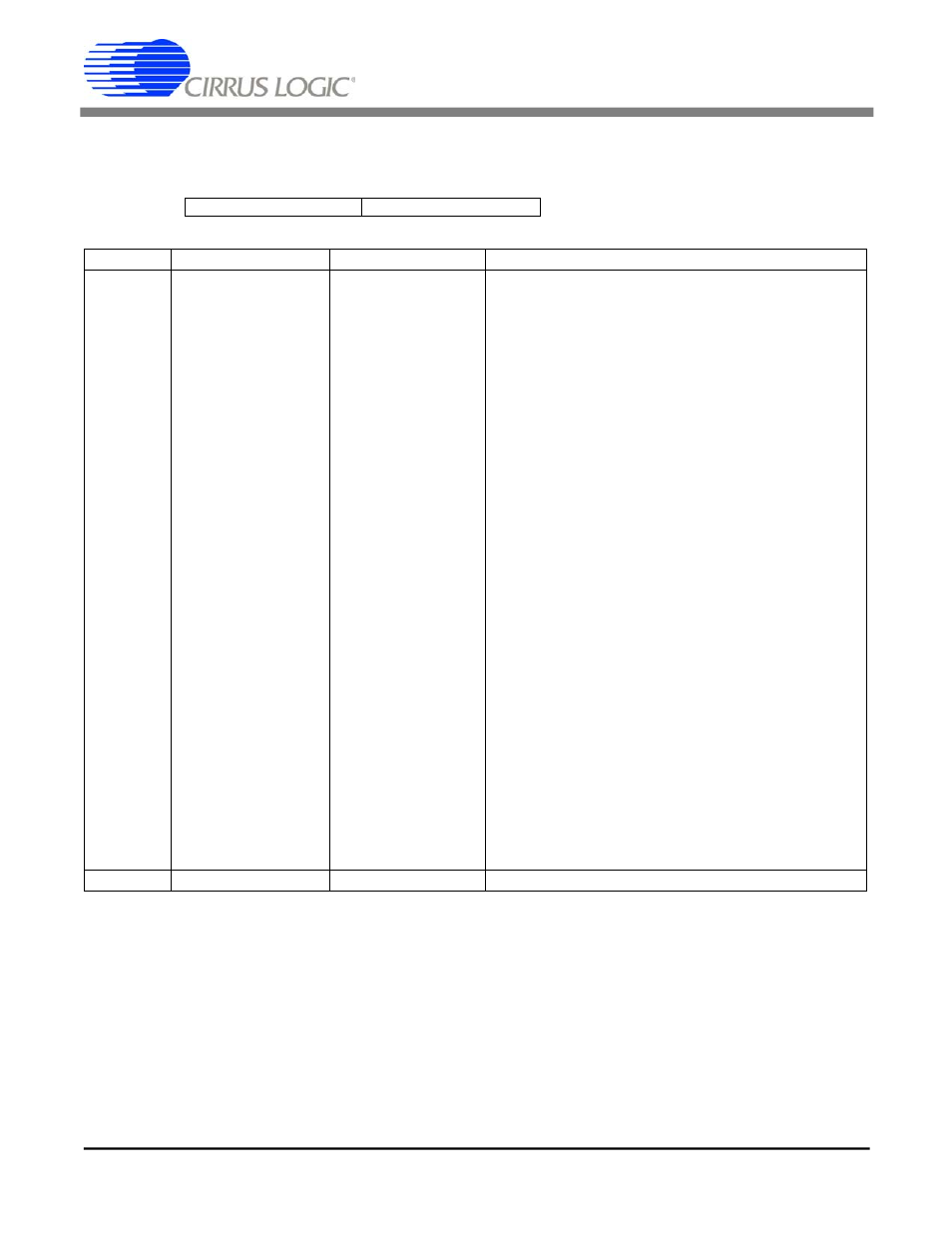

Cs8130, Control data byte format – Cirrus Logic CS8130 User Manual

Page 13

BIT

NAME

VALUE

FUNCTION

AD3-0

Register Address

(4 bits of

transmitted address

+ MSB, which is the

shadow (SHDW) bit

state [Control Reg

#3]. All registers

have 4 data bits).

0_0000

0_0001

0_0010

0_0011

0_0100

0_0101

0_0110

0_0111

0_1000

0_1001

0_1010

0_1011

0_1100

0_1101

0_1110

0_1111

1_0000

1_0001

1_0010

1_0011

1_0100

1_0101

1_0110

1_0111

1_1000

1_1001

1_1010

1_1011

1_1100

1_1101

1_1110

1_1111

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Control register #1

Control register #2

Transmit Mode Register #1

Transmit Mode Register #2

Output Power register

Receive Mode register

Receive Sensitivity register #1

Receive Sensitivity register #2

Baud Rate Divider register #1

Baud Rate Divider register #2

Modulator Divider register #1

Modulator Divider register #2

Digital Output Pin Control register

Control Register #3

Reserved

Status register (read only)

TV Remote Receive Sample Rate & T Period Divider

TV Remote Receive Sample Rate & T Period Divider

TV Remote Receive Sample Rate & T Period Divider

TV Remote Transmit Bit Rate Divider #1

TV Remote Transmit Bit Rate Divider #2

Control Register #4

Reserved

Reserved

ASK Receive Timing Sensitivity register

Reserved

Reserved

Reserved

CS8130 Revision Level register (Read Only)

Reserved

Reserved (Resets to 1111; must not be changed)

Reserved (Resets to 1111; must not be changed)

CD3-0

Control Data

Contains control register data.

It is essential that all reserved registers and bits are not changed from their reset state. If reserved bits

are changed, then internal test modes may be invoked, which may change some input pins to output

pins, and may completely change the definition of some functions and signals. Reserved bits in regis-

ters, and reserved registers, may not return a known state when read, and should be ignored. Registers

28 and 15 are read only. Other non-reserved registers are write only. The CS8130 can be set to echo

back register write commands to verify correct reception of the control settings.

Control Data Byte Format

D7

D6

D5

D4

D3

D2

D1

D0

AD3

AD2

AD1

AD0

CD3

CD2

CD1

CD0

CS8130

DS134PP2

13

CS8130

DS134F1

13