Cirrus Logic CS61584A User Manual

Preliminary product information, Features, Description

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

Cirrus Logic, Inc. 2000

(All Rights Reserved)

s 78760

5 7581

http://www.cirrus.com

Features

l

Dual T1/E1 Line Interface

l

3.3 Volt and 5 Volt Versions

l

Crystal-less Jitter Attenuator Meets

European CTR 12 and ETSI ETS 300 011

Specifications

l

Matched Impedance Transmit Drivers

l

Transmitter Tri-state Capability

l

Common Transmit and

ReceiveTransformers for all Modes

l

Serial and Parallel Host Mode Operation

l

User-customizable Pulse Shapes

l

Supports JTAG Boundary Scan

l

Compliant with:

– ITU-T Recommendations: G.703, G.704,

G.706, G.732, G.775 and I.431

– American National Standards (ANSI): T1.102,

T1.105, T1.403, T1.408, and T1.231

– FCC Rules and Regulations: Part 68 and Part

15

– AT&T Publication 62411

– ETSI ETS 300 011, 300 233, CTR 12, TBR 13

l

TR-NET-00499

Description

The CS61584A is a dual line interface for T1/E1 appli-

cations, designed for high-volume cards where low

power and high density are required. The device is op-

timized for flexible microprocessor control through a

serial or parallel Host mode interface. Hardware mode

operation is also available.

Matched impedance drivers reduce power consumption

and provide substantial transmitter return loss. The

transmitter pulse shapes are customizable to allow non-

standard line loads. Crystalless jitter attenuation com-

plies with most stringent standards. Support of JTAG

boundary scan enhances system testability and

reliability.

CS61584A-IQ3:3.3V, 64-pin TQFP, -40 to +85° C

CS61584A-IL5:5.0V, 68-pin PLCC, -40 to +85° C

CS61584A-IQ5:5.0V, 64-pin TQFP, -40 to +85° C

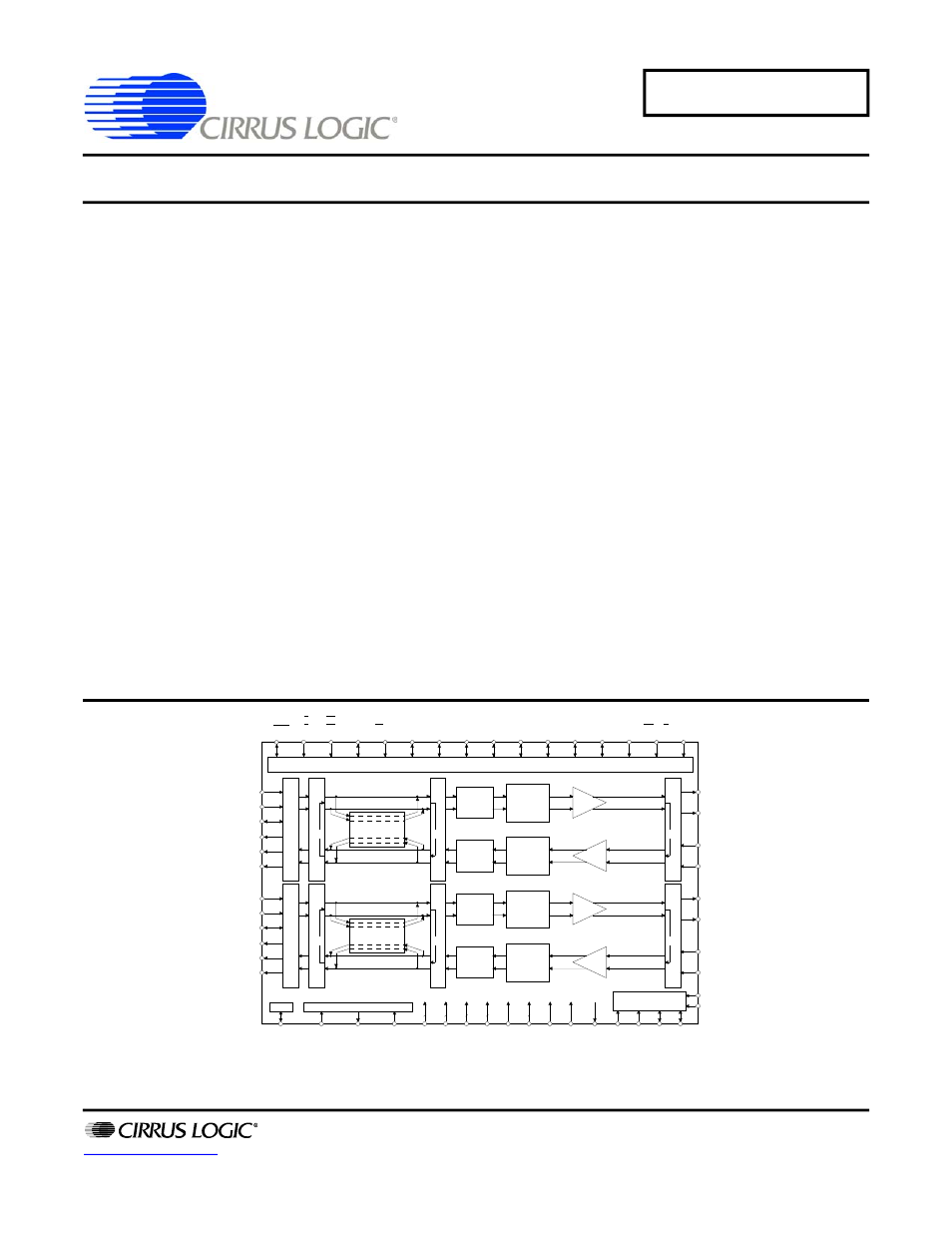

TTIP1

TRING1

RRING1

RTIP1

DRIVER

CONTROL

TCLK1

RCLK1

RESET

JTAG

4

REFCLK

XTALOUT

1XCLK

TV+ TGND RV+ RGND DV+ DGND

CLOCK GENERATOR

Serial Port

Parallel Port

Hardware Mode

INT

INT

RLOOP1

SCLK

RD(DS)

RLOOP2

SDO

AD0

LLOOP

SDI

AD1

TAOS1

AD3

CON01

AD4

CON02

AD5

CON11

AD6

CON12

AD7

CON21

ALE(AS)

CON22

BTS

CON32

(TDATA1) TPOS1

(AIS1) TNEG1

(RDATA1) RPOS1

(BPV1) RNEG1

L

O

C

A

L

L

O

O

P

B

A

C

K

2

AV+ AGND BGREF

MODE

WR(R/W)

CON31

SPOL

AD2

TAOS2

PD1

SAD4

ZTX1

PD2

SAD5

ZTX2

LOS1

SAD6

LOS1

LOS2

SAD7

LOS2

PULSE

SHAPING

CIRCUITRY

CLOCK &

DATA

RECOVERY

LOS &

AIS

DETECT

JITTER

ATTENUATOR

P/S

P/S

ATTEN0

CS

CS

ATTEN1

TAOS

E

N

C

O

D

E

R

D

E

C

O

D

E

R

CONTROL

Hardware Mode

Parallel Port

Serial Port

L

O

C

A

L

L

O

O

P

B

A

C

K

1

R

E

M

O

T

E

L

O

O

P

B

A

C

K

TTIP2

TRING2

RRING2

RTIP2

DRIVER

TCLK2

RCLK2

(TDATA2) TPOS2

(AIS2) TNEG2

(RDATA2) RPOS2

(BPV2) RNEG2

L

O

C

A

L

L

O

O

P

B

A

C

K

2

PULSE

SHAPING

CIRCUITRY

CLOCK &

DATA

RECOVERY

LOS &

AIS

DETECT

JITTER

ATTENUATOR

TAOS

E

N

C

O

D

E

R

D

E

C

O

D

E

R

L

O

C

A

L

L

O

O

P

B

A

C

K

1

R

E

M

O

T

E

L

O

O

P

B

A

C

K

2

2

2

2

3

RECEIVER

RECEIVER

IPOL (DTACK)

CLKE

IPOL

Dual T1/E1 Line Interface

JAN ‘01

DS261PP5

CS61584A

Copyright

Cirrus Logic, Inc. 2005

(All Rights Reserved)

CS61584A

Dual T1/E1 Line Interface

SEP ‘05

DS261F1

Document Outline

- CS61584A

- Features

- Description

- TABLE OF CONTENTS

- LIST OF TABLES

- LIST OF FIGURES

- 1. CHARACTERISTICS AND SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- RECOMMENDED OPERATING CONDITIONS

- ANALOG CHARACTERISTICS

- DIGITAL CHARACTERISTICS

- SWITCHING CHARACTERISTICS

- SWITCHING CHARACTERISTICS - SERIAL PORT

- SWITCHING CHARACTERISTICS - PARALLEL PORT

- Figure 6. Parallel Port Timing - Motorola Mode

- Figure 7. Parallel Port Timing - Intel Read Mode

- Figure 8. Parallel Port Timing - Intel Write Mode

- Figure 9. Parallel Port Timing - Motorola Mode to RAM

- Figure 10. Parallel Port Timing - Intel Read Mode from RAM or ROM

- Figure 11. Parallel Port Timing - Intel Write Mode to RAM

- SWITCHING CHARACTERISTICS - JTAG

- 2. OVERVIEW

- 3. TRANSMITTER

- 4. RECEIVER

- 5. JITTER ATTENUATOR

- 6. REFERENCE CLOCK

- 7. POWER-UP RESET

- 8. LINE CONTROL AND MONITORING

- 9. HOST MODE

- 10. JTAG BOUNDARY SCAN

- Figure 23. JTAG Circuitry Block Diagram

- 10.1 JTAG Data Registers (DR)

- 10.2 JTAG Instructions and Instruction Register (IR)

- 10.3 JTAG TAP Controller

- 10.4 Test-Logic-Reset State

- 10.5 Run-Test/Idle State

- 10.6 Select-DR-Scan State

- 10.7 Capture-DR State

- 10.8 Shift-DR State

- 10.9 Exit1-DR State

- 10.10 Pause-DR State

- 10.11 Exit2-DR State

- 10.12 Update-DR State

- 10.13 Select-IR-Scan State

- 10.14 Capture-IR State

- 10.15 Shift-IR State

- 10.16 Exit1-IR State

- 10.17 Pause-IR State

- 10.18 Exit2-IR State

- 10.19 Update-IR State

- 10.20 JTAG Application Examples

- 11. PIN DESCRIPTIONS

- 12. PACKAGE DIMENSIONS

- 13. APPLICATIONS

- Ordering Information