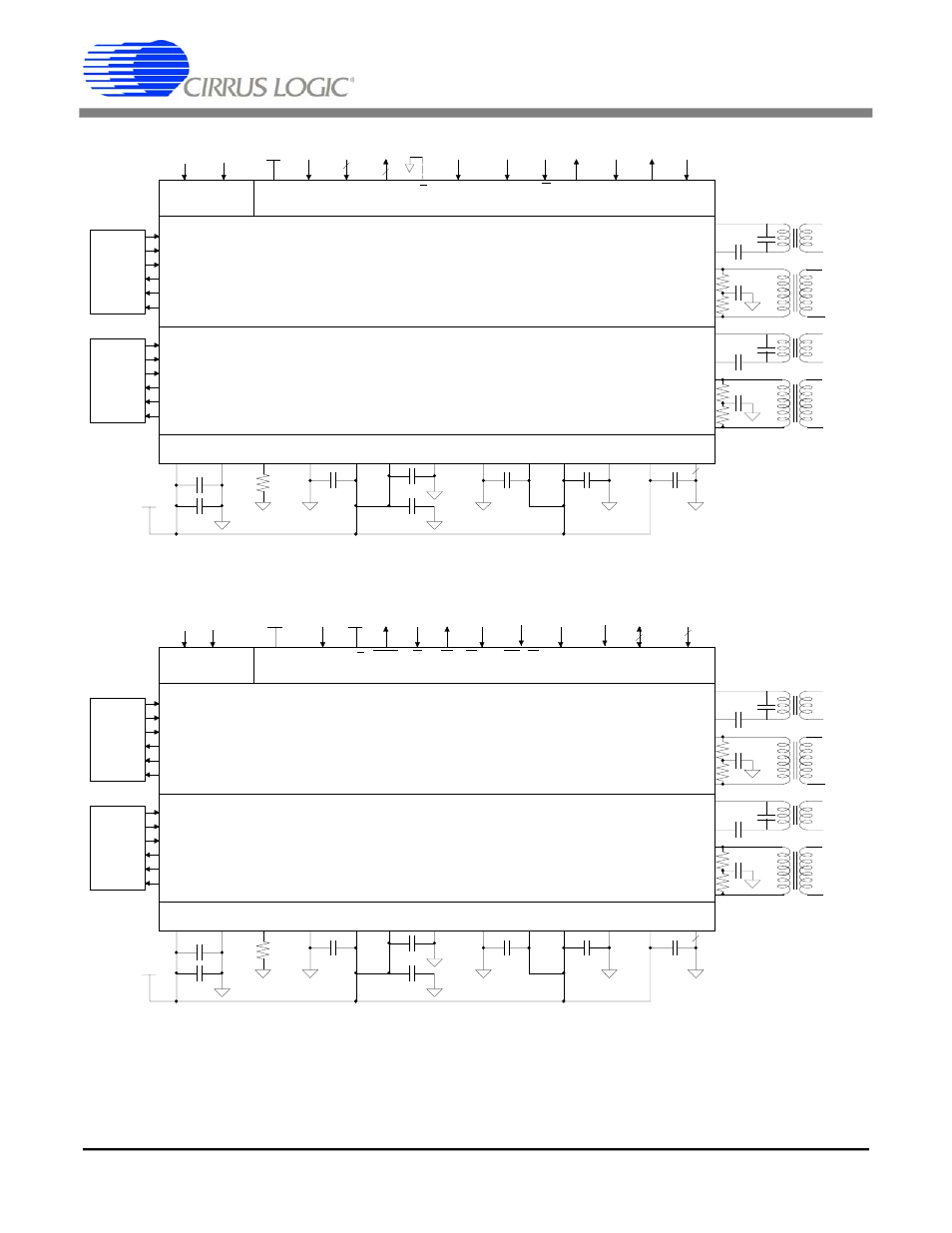

Figure 28. host mode serial port configuration, Figure 29. host mode parallel port configuration, Ds261pp5 – Cirrus Logic CS61584A User Manual

Page 49

CS61584A

DS261PP5

49

DS261PP5

AV+

AGND

BGREF

TV+1

TGND1

RV+1

RGND1 DV+ DGND1:3

0.01

µ

F

TCLK1

TPOS1 (TDATA1)

TNEG1 (AIS1)

RCLK1

RPOS1 (RDATA1)

RNEG1 (BPV1)

TCLK2

TPOS2 (TDATA2)

TNEG2 (AIS2)

RCLK2

RPOS2 (RDATA2)

RNEG2 (BPV2)

Framer

Framer

TTIP1

TRING1

RTIP1

RRING1

TTIP2

TRING2

RTIP2

RRING2

Host Control

Power Supply

Clock Generator

Channel 2

Channel 1

transmit

transmit

3

0.1

µ

F

1

µ

F

+

0.1

µ

F

TV+2

TGND2

RV+2

RGND2

22

µ

F

+

0.1

µ

F

0.1

µ

F

0.1

µ

F

receive

R3

R4

receive

R1

R2

R3

4.99k

Ω

V

CC

0.47

µ

F

0.47

µ

F

REFCLK 1XCLK

C1

C2

0.47

µ

F

0.47

µ

F

IPOL

P/S

CS

INT

SCLK

SDO

SDI

SPOL

Vcc

RESET

MODE

LOS[1:2]

2

T1

T2

T3

T4

1:N

1:N

1:N

1:N

ZTX[1:2]

2

Figure 28. Host Mode Serial Port Configuration

AV+

AGND

BGREF

TV+1

TGND1

RV+1

RGND1 DV+ DGND1:3

0.01

µ

F

TCLK1

TPOS1 (TDATA1)

TNEG1 (AIS1)

RCLK1

RPOS1 (RDATA1)

RNEG1 (BPV1)

TCLK2

TPOS2 (TDATA2)

TNEG2 (AIS2)

RCLK2

RPOS2 (RDATA2)

RNEG2 (BPV2)

Framer

Framer

TTIP1

TRING1

RTIP1

RRING1

TTIP2

TRING2

RTIP2

RRING2

Host Control

Power Supply

Clock Generator

Channel 2

Channel 1

transmit

transmit

3

0.1

µ

F

1

µ

F

+

0.1

µ

F

TV+2

TGND2

RV+2

RGND2

22

µ

F

+

0.1

µ

F

0.1

µ

F

0.1

µ

F

receive

R3

R4

receive

R1

R2

R3

4.99k

Ω

V

CC

0.47

µ

F

0.47

µ

F

REFCLK 1XCLK

C1

C2

0.47

µ

F

0.47

µ

F

DTACK

P/S

CS

INT

Vcc

RESET

MODE

RD(DS)

AD[0:7]

ALE(AS)

WR(R/W)

BTS

SAD[4:7]

Vcc

7

4

T1

T2

T3

T4

1:N

1:N

1:N

1:N

Figure 29. Host Mode Parallel Port Configuration

CS61584A

DS261F1

49