Cirrus Logic CS5513 User Manual

Adcs, Features, General description

Copyright

Cirrus Logic, Inc. 2009

(All Rights Reserved)

CS5510/11/12/13

16-bit and 20-bit, 8-pin

ΔΣ

ADCs

Features

Delta-sigma Analog-to-digital Converter

– Linearity Error: 0.0015% FS

– Noise-free Resolution: Up to 17 Bits

Differential Bipolar Analog Inputs

V

REF

Input Range from 250 mV to 5 V

50/60 Hz Simultaneous Rejection

(CS5510/12)

16 to 326 Sps Output Word Rate

On-chip Oscillator (CS5511/13)

Power Supply Configurations:

– V+ = 5 V, V- = 0 V

– Multiple Dual-supply Arrangements

Low Power Consumption

– Normal Mode, 2.5 mW

– Sleep Mode, 10

μW

Low-cost, Compact, 8-pin Package

Lead-free Device Package Options

General Description

The CS5510/11/12/13 are low-cost, easy-to-use,

ΔΣ an-

alog-to-digital converters (ADCs) which use charge-

balance techniques to achieve 16-bit (CS5510/11) and

20-bit (CS5512/13) performance. The ADCs are avail-

able in a space-efficient, 8-pin SOIC package and are

optimized for measuring signals in weigh scale, process

control, and other industrial applications.

To accommodate these applications, the ADCs include

a fourth-order

ΔΣ modulator and a digital filter. When

configured with an external master clock of 32.768 kHz,

the filter in the CS5510/12 provides better than 80 dB of

simultaneous 50 and 60 Hz line rejection, and outputs

conversion words at 53.5 Sps. The CS5511/13 include

an on-chip oscillator which eliminates the need for an ex-

ternal clock source.

Low-power, flexible supply configurations, compact pi-

nout, and ease of use make these products ideal

solutions for cost-conscience and space-constrained

applications.

ORDERING INFORMATION

See

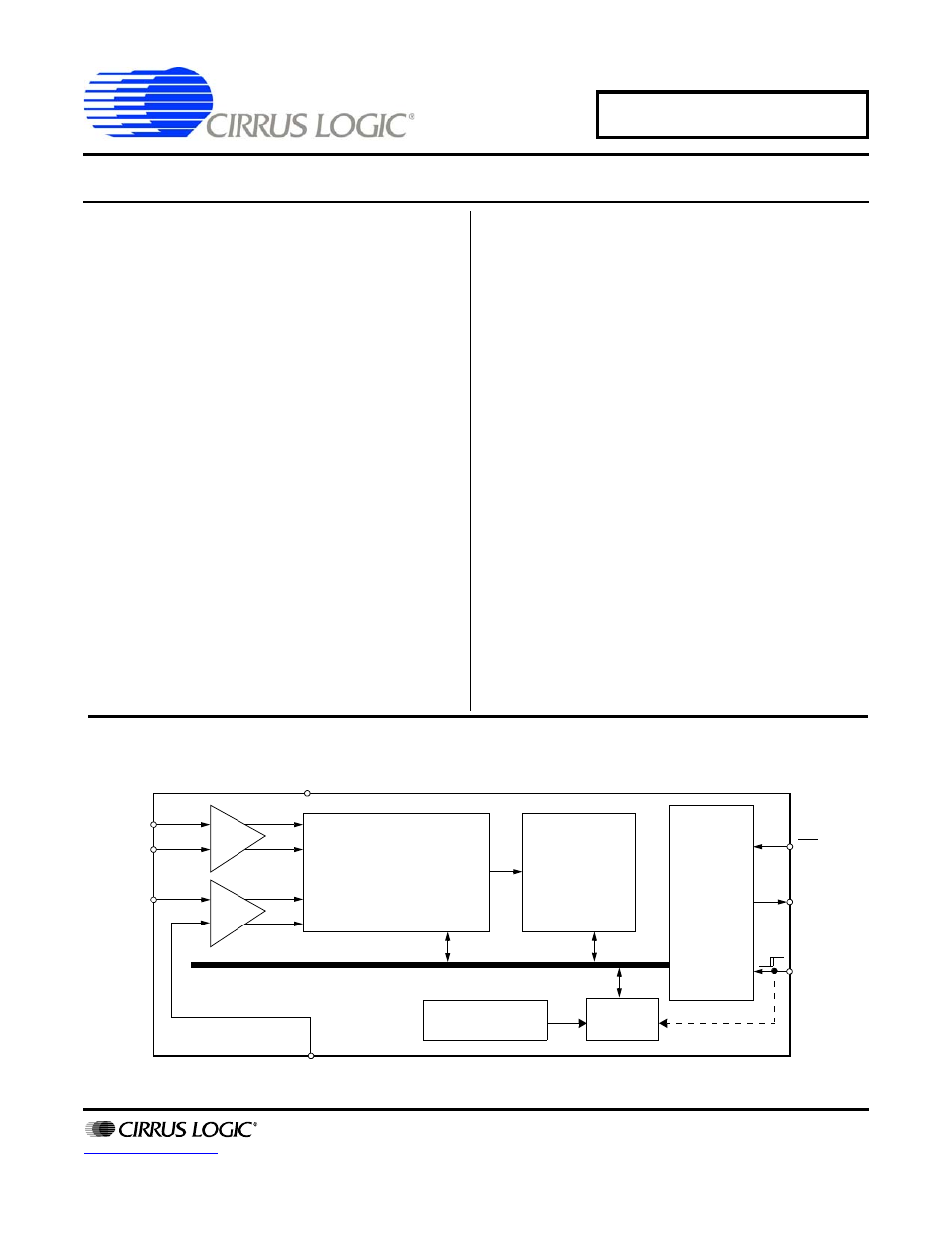

V+

AIN+

AIN-

VREF

Clock

Gen.

1X

~0.8X

Differential

4th-order

Delta-sigma

Modulator

Digital Filter

Control

Output

SCLK

SDO

Logic

Oscillator

(CS5511/13 only)

V-

(CS5510/12 only)

CS

JUL ‘09

DS337F4

Document Outline

- Features & Description

- Table of Contents

- List of Figures

- List of Tables

- 1. Characteristics and Specifications

- 2. General Description

- 3. Pin Descriptions

- 4. Specification Definitions

- 5. Ordering Information

- 6. Environmental, Manufacturing, & Handling Information

- 7. Package Dimensions

- 8. Revision History