7 adcx input select, invert & mute (address 07h), Figure 21. ain & pga selection, Figure 21.ain & pga selection – Cirrus Logic CS53L21 User Manual

Page 47: Adcx, Adcx input select, invert & mute (address 07h)” on, P 47, Cs53l21

DS700PP1

47

CS53L21

6.7

ADCx Input Select, Invert & Mute (Address 07h)

ADCX Input Select Bits (AINX_MUX[1:0])

Default: 00

Function:

Selects the specified analog input signal into ADCx. The microphone pre-amplifier is only available when

PDN_PGAx is disabled. See

ADCX Invert Signal Polarity (INV_ADCX)

Default: 0

0 - Disabled

1 - Enabled

Function:

When enabled, this bit will invert the signal polarity of the ADC x channel.

ADCX Channel Mute (ADCX_MUTE)

Default: 0

0 - Disabled

1 - Enabled

Function:

The output of channel x ADC will mute when enabled. The muting function is affected by the ADCx Soft bit

(SOFT).

7

6

5

4

3

2

1

0

AINB_MUX1

AINB_MUX0

AINA_MUX1

AINA_MUX0

INV_ADCB

INV_ADCA

ADCB_MUTE ADCA_MUTE

PDN_PGAx AINx_MUX[1:0]

Selected Path to ADC

0

00

AIN1x-->PGAx

0

01

AIN2x-->PGAx

0

10

AIN3x/MICINx-->PGAx

0

11

AIN3x/MICINx-->Pre-Amp

(+16/+32 dB Gain)

-->PGAx

1

00

AIN1x

1

01

AIN2x

1

10

AIN3x/MICINx

1

11

Reserved

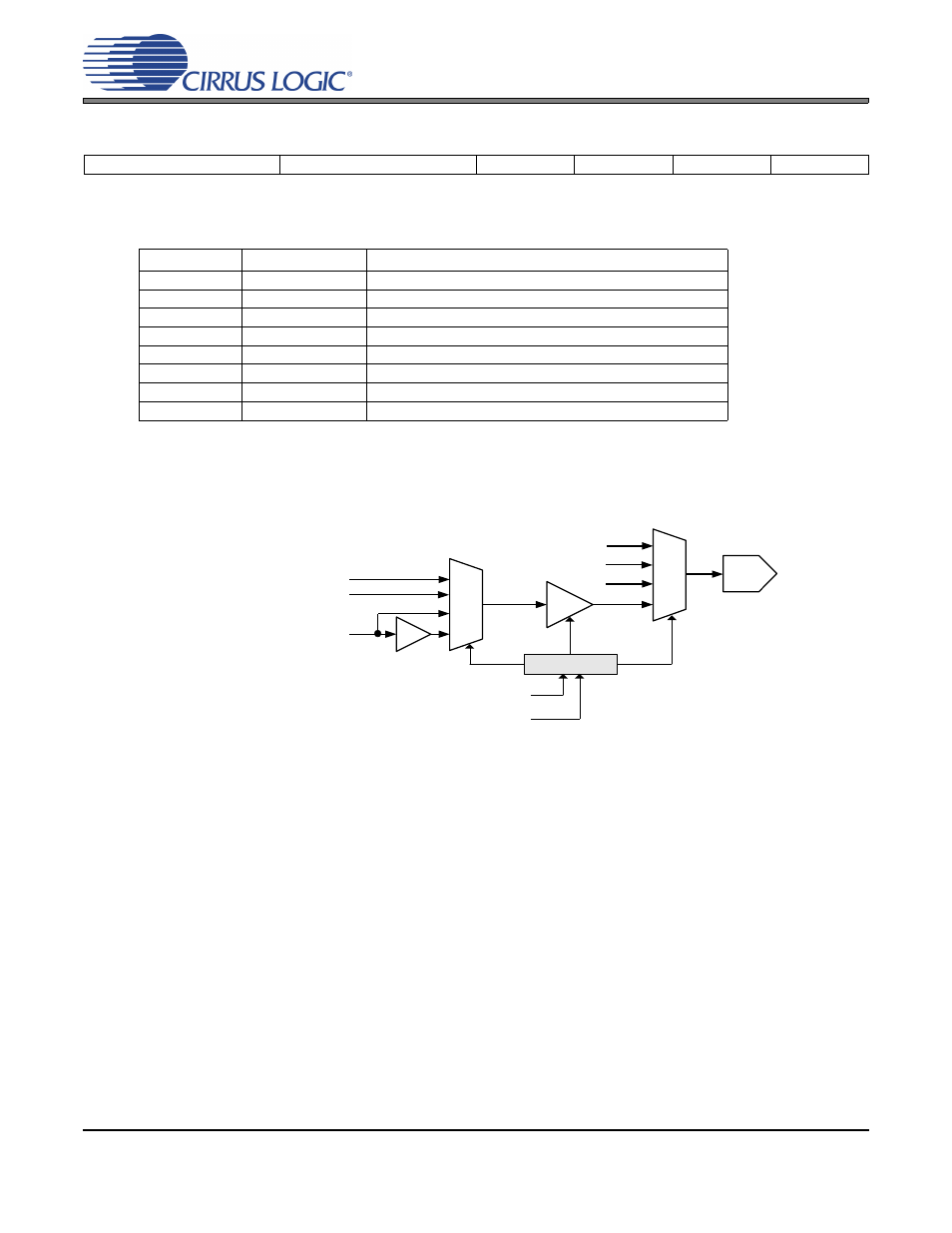

MUX

AIN1x

AIN2x

AIN3x / MICINx

PGA

+16/

32 dB

MUX

AINx_MUX[1:0]

PDN_PGAx

AIN1x

AIN2x

AIN3x

Decoder

ADC

Figure 21. AIN & PGA Selection