8 noise gate, Figure 11. noise gate attenuation, Figure 11.noise gate attenuation – Cirrus Logic CS53L21 User Manual

Page 27: Cs53l21

DS700PP1

27

CS53L21

4.3.8

Noise Gate

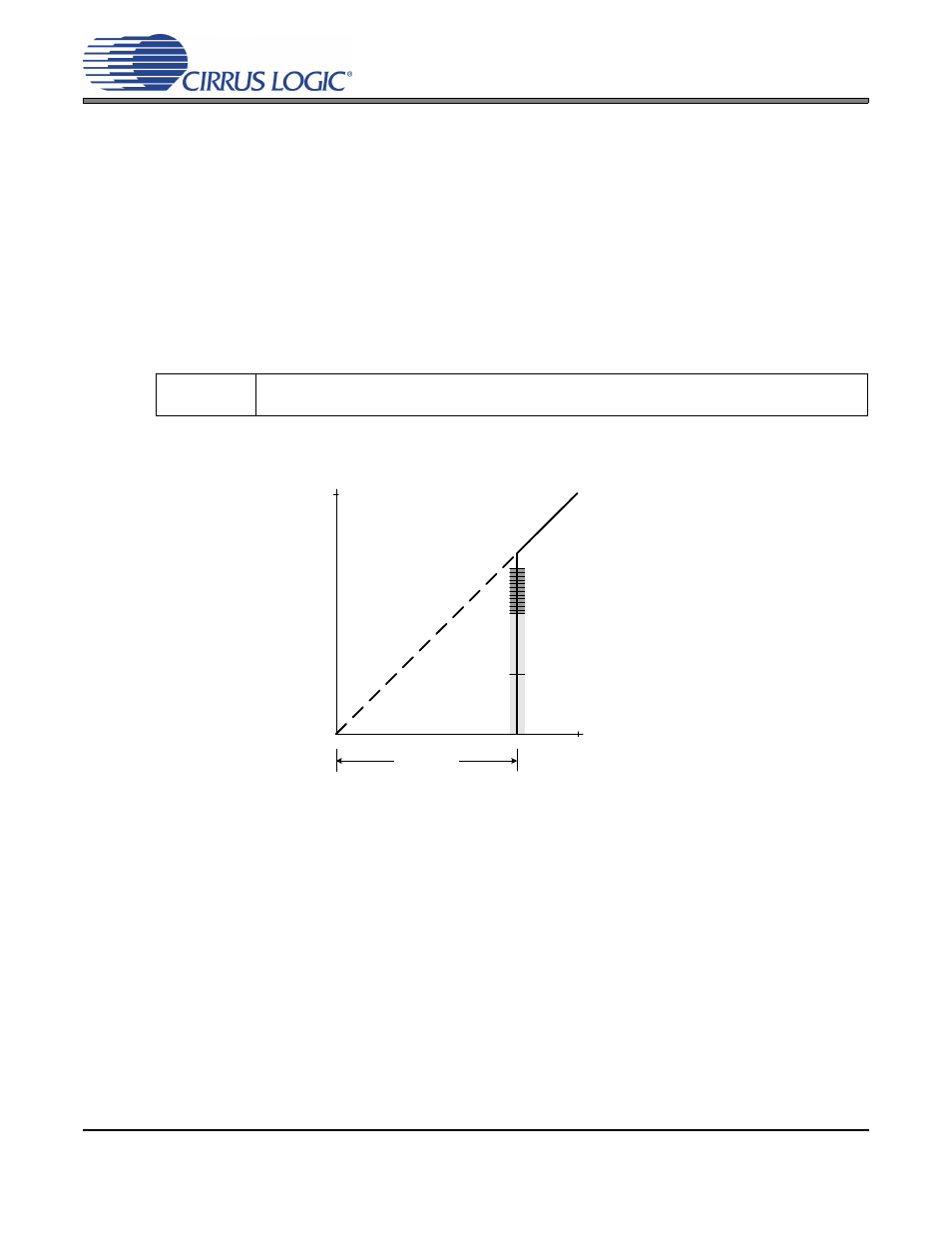

The noise gate may be used to mute signal levels that fall below a programmable threshold. This prevents

the ALC from applying gain to noise. A programmable delay may be used to set the minimum time before

the noise gate attacks the signal.

Maximum noise gate attenuation levels will depend on the gain applied in either the PGA or MIC pre-am-

plifier. For example: If both +32 dB pre-amplification and +12 dB programmable gain is applied, the max-

imum attenuation that the noise gate achieves will be 52 dB (-96 + 32 + 12) below full-scale.

Ramp-down time to the maximum setting is affected by the SOFTx bit.

Recommended settings: For best results, enable soft ramp for the digital attenuator. When the analog in-

puts are configured for differential signals (see

“Differential Inputs” on page 23“Differential Inputs” on

), enable the NG_ALL bit to trigger the noise gate only when both inputs fall below the threshold.

Software

Controls:

“Noise Gate Configuration & Misc. (Address 1Fh)” on page 54

“ADC Control (Address 06h)” on

.

-96

-40

THRESH[2:0]

Max

imum A

tte

n

ua

tio

n

*

-52 dB

Output

(dB)

Input (dB)

NG

EN

=1

NG

EN

=0

-80 dB

-64 dB

Figure 11. Noise Gate Attenuation