4 hardware functional description, 1 coyote 32-bit dsp core, 1 dsp memory – Cirrus Logic CS4953xx User Manual

Page 7: 2 dma controller

CS4953xx Data Sheet

32-bit Audio Decoder DSP Family

DS705F2

7

4 Hardware Functional Description

4.1 Coyote 32-bit DSP Core

The CS4953xx is a dual-core DSP with separate X and Y data and P code memory spaces. Each core is a

high-performance, 32-bit, user-programmable, fixed-point DSP that is capable of performing two multiply

accumulate (MAC) operations per clock cycle. Each core has eight 72-bit accumulators, four X- and four Y-data

registers, and 12 index registers.

Both DSP cores are coupled to a flexible DMA engine. The DMA engine can move data between peripherals

such as the digital audio input (DAI) and digital audio output (DAO), external memory, or any DSP core

memory, all without the intervention of the DSP. The DMA engine offloads data move instructions from the DSP

core, leaving more MIPS available for signal processing instructions.

CS4953xx functionality is controlled by application codes that are stored in on-board ROM or downloaded to

the CS4953xx from a host MCU or external FLASH/EEPROM. Users can choose to use standard audio

decoder and post-processor modules which are available from Cirrus Logic.

The CS4953xx is suitable for audio decoder, audio post-processor, audio encoder, DVD audio/video player,

and digital broadcast decoder applications.

4.1.1 DSP Memory

Each DSP core has its own on-chip data and program RAM and ROM and does not require external memory

for any of today’s popular audio algorithms including Dolby Digital Surround EX, AAC Multichannel, DTS-ES

96/24, and THX Ultra2.

The memory maps for the DSPs are as follows. All memory sizes are composed of 32-bit words.

4.1.2 DMA Controller

The powerful 12-channel DMA controller can move data between eight on-chip resources. Each resource has

its own arbiter: X, Y, and P RAM/ROMs on DSP A; X, Y, and P RAM/ROMs on DSP B; external memory; and

the peripheral bus. Modulo and linear addressing modes are supported, with flexible start address and

increment controls. The service interval for each DMA channel as well as up to six interrupt events, is

programmable.

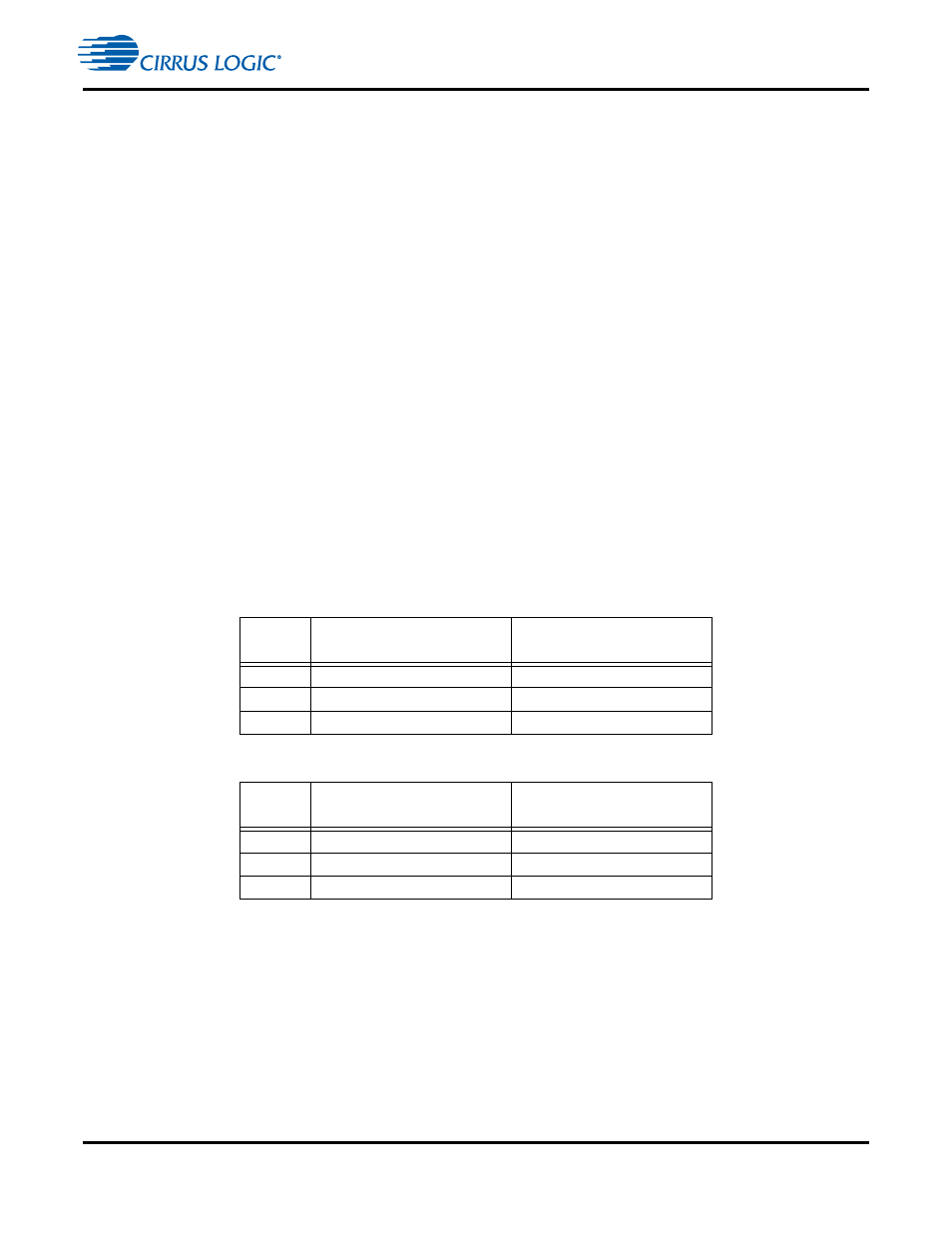

Table 3. CS49530x DSP Memory Sizes

Memory

Type

DSP A

DSP B

X

16K SRAM, 16K ROM

10K SRAM, 8K ROM

Y

16K SRAM, 32K ROM

16K SRAM, 16K ROM

P

8K SRAM, 32K ROM

8K SRAM, 24K ROM

Table 4. CS49531x DSP Memory Sizes

Memory

Type

DSP A

DSP B

X

16K SRAM, 16K ROM

10K SRAM, 8K ROM

Y

24K SRAM, 32K ROM

16K SRAM, 16K ROM

P

8K SRAM, 32K ROM

8K SRAM, 24K ROM