Cirrus Logic CS4953xx User Manual

Page 36

CS4953xx Data Sheet

32-bit Audio Decoder DSP Family

DS705F2

36

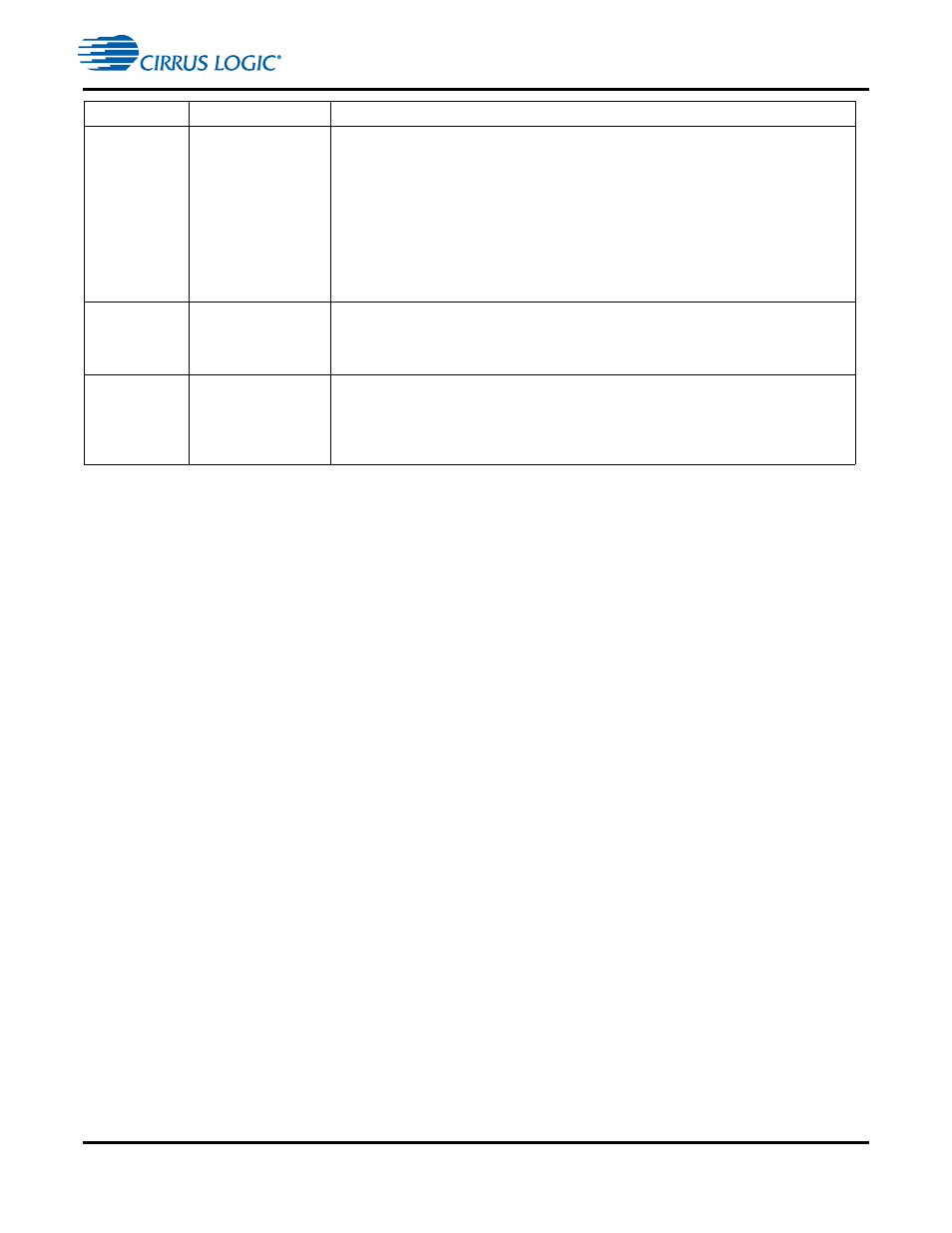

PP8

April, 2011

Added Tj conditions to

Changed 500 ma to 350 ma in

Removed references to DSD.

Updated legal statement.

Updated features list.

Added notes to

.

Section 5.16 “Switching Characteristics — Digital Audio Slave Input Port”

Section 5.17 “Switching Characteristics — Digital Audio Output Port” on

PP9

August, 2011

, added Max value of DCLK frequency value in

CS49530x-DVZ and CS49531x-DVZ to 130 MHz; added Min value of DCLK period

in CS49530x-DVZ and CS49531x-DVZ to 7.7 ns. Added notes to

PP10

February, 2012

Updated trademark information throughout document and boilerplate. Updated max

Fdclk value for DVZ parts to 131 MHz and min DCLK value for DVZ parts to 7.63 ns

in

. Updated tspickl and tspickh minimum values in

tdaisstlr and tdaislrts to

. Changed max spec of Tdaosdv in

. Updated Tsddh minimum value in

.

Revision

Date

Changes