2 noise gate enable, 3 noise gate threshold and boost, 4 noise gate delay timing – Cirrus Logic CS42L55 User Manual

Page 65: 1 alcx soft ramp disable, 2 alcx zero cross disable, P 65, Alcx zero cross disable” on, Cs42l55

DS773F1

65

CS42L55

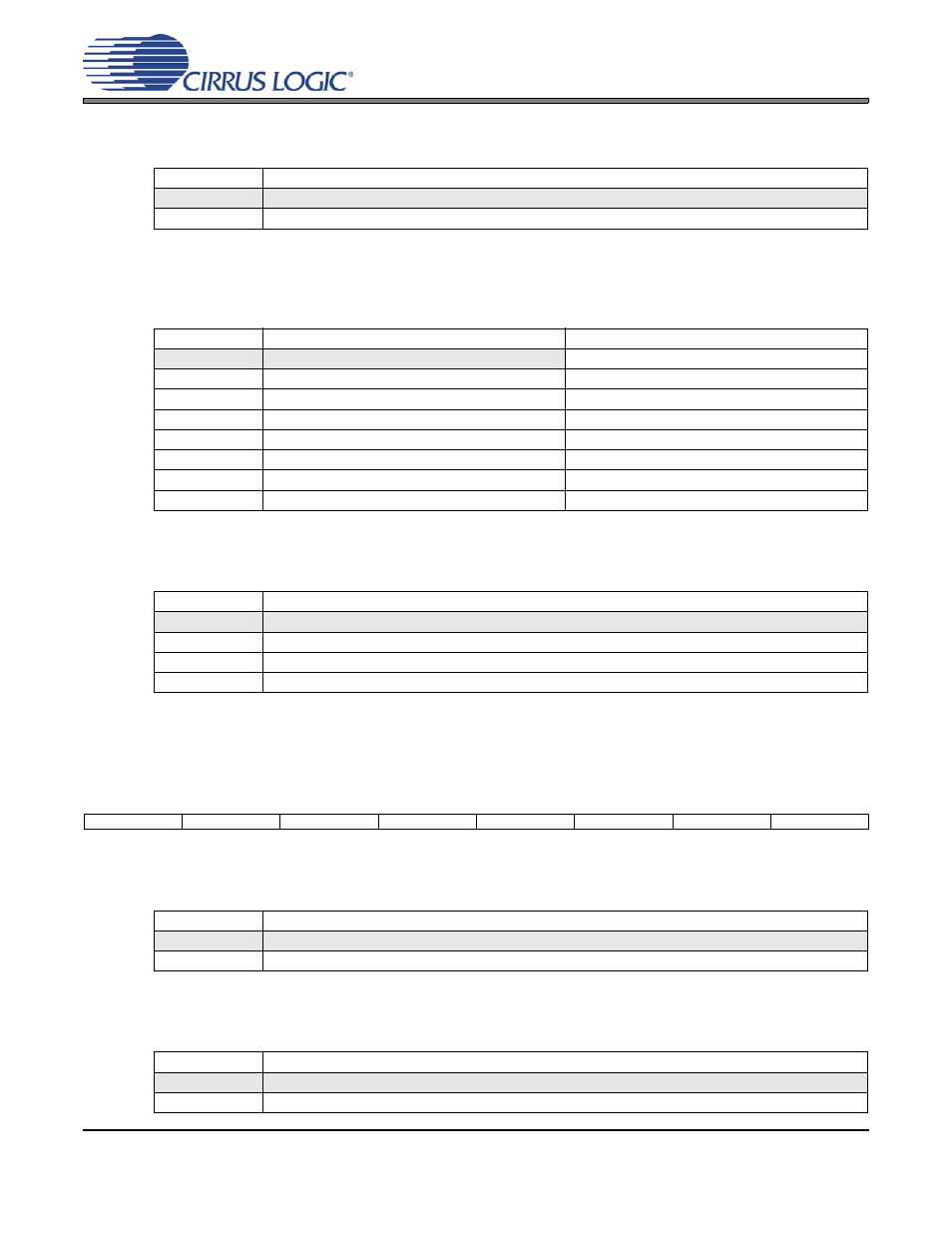

6.32.2

Noise Gate Enable

Configures the noise gate.

6.32.3

Noise Gate Threshold and Boost

THRESH sets the threshold level of the noise gate. Input signals below the threshold level will be attenu-

ated to -96 dB. NG_BOOST configures a +30 dB boost to the threshold settings.

6.32.4

Noise Gate Delay Timing

Sets the delay time before the noise gate attacks.

Note:

The Noise Gate attack rate is a function of the sampling frequency, Fs, and the DIGSFT (

) setting unless the disable bit (

“ALCx Soft Ramp Disable” on page 65

) is enabled.

6.33

ALC and Limiter Soft Ramp, Zero Cross Disables (Address 28h)

6.33.1

ALCx Soft Ramp Disable

Configures an override of the analog soft ramp setting.

6.33.2

ALCx Zero Cross Disable

Configures an override of the analog zero cross setting.

NG

Noise Gate Status

0

Disabled

1

Enabled

THRESH[2:0]

Minimum Setting (NG_BOOST = ‘0’b)

Minimum Setting (NG_BOOST = ‘1’b)

000

-64 dB

-34 dB

001

-67 dB

-36 dB

010

-70 dB

-40 dB

011

-73 dB

-43 dB

100

-76 dB

-46 dB

101

-82 dB

-52 dB

110

Reserved

-58 dB

111

Reserved

-64 dB

NGDELAY[1:0]

Delay Setting

00

50 ms

01

100 ms

10

150 ms

11

200 ms

7

6

5

4

3

2

1

0

ALCBSRDIS

ALCBZCDIS

ALCASRDIS

ALCAZCDIS

LIMSRDIS

Reserved

Reserved

ALCxSRDIS

ALC Soft Ramp Disable

0

OFF; ALC Attack Rate is dictated by the DIGSFT (

“Digital Soft Ramp” on page 46

) setting

1

ON; ALC volume changes take effect in one step, regardless of the DIGSFT setting.

ALCxZCDIS

ALC Zero Cross Disable

0

OFF; ALC Attack Rate is dictated by the ANLGZC (

“Analog Zero Cross” on page 46

1

ON; ALC volume changes take effect at any time, regardless of the ANLGZC setting.