2 analog zero cross, 3 digital soft ramp, 4 freeze registers – Cirrus Logic CS42L55 User Manual

Page 46: 8 adc, line, hp mux (address 08h), 1 adc x input select, P 46, Cs42l55

46

DS773F1

CS42L55

6.7.2

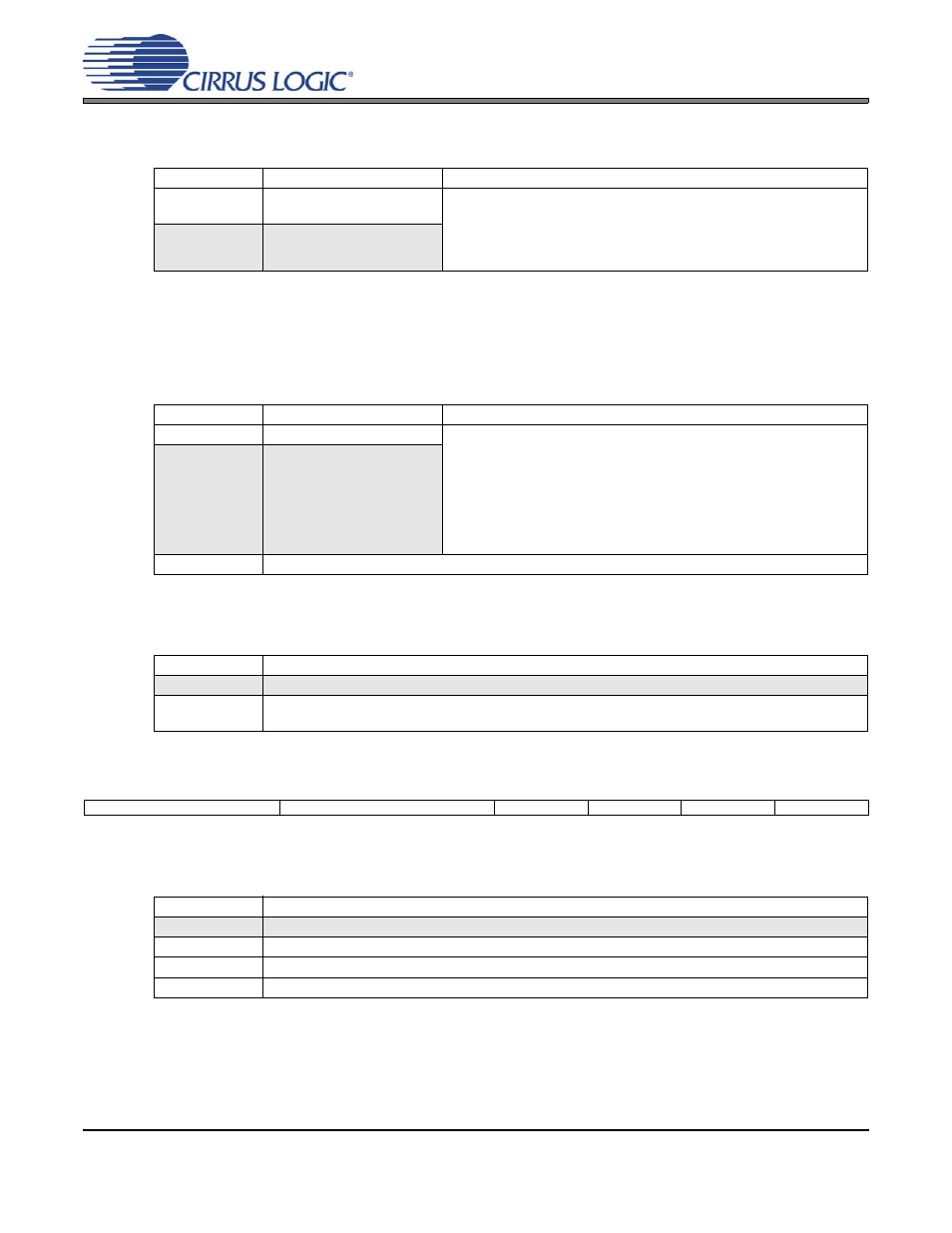

Analog Zero Cross

Configures when the signal level changes occur for the analog volume controls.

Note:

If the signal does not encounter a zero crossing, the requested volume change will occur after a

timeout period of 1024 sample periods (approximately 10.7 ms at 48 kHz sample rate).

6.7.3

Digital Soft Ramp

Configures an incremental volume ramp from the current level to the new level at the specified rate.

6.7.4

Freeze Registers

Configures a hold on all register settings.

6.8

ADC, Line, HP MUX (Address 08h)

6.8.1

ADC x Input Select

Selects the specified analog input signal into ADCx.

Note:

Pseudo-differential inputs are not available when the PGA is bypassed.

ANLGZCx

Volume Changes

Affected Analog Volume Controls

0

Do not occur on a zero cross-

ing

PGAx_VOL[5:0] (

)

HPxMUTE (

“Headphone Channel x Mute” on page 57

)

HPxVOL[6:0] (

“Headphone Volume Control” on page 57

“Line Channel x Mute” on page 58

LINExVOL[6:0] (

“Line Volume Control” on page 58

)

1

Occur on a zero crossing

DIGSFT

Volume Changes

Affected Digital Volume Controls

0

Do not occur with a soft ramp

ADCxMUTE (

ADCxATT[7:0] (

AMIXxMUTE (

“ADC Mixer Channel x Mute” on page 51

)

AMIXxVOL[6:0] (

“ADC Mixer Channel x Volume” on page 51

PMIXxMUTE (

“PCM Mixer Channel x Mute” on page 52

PMIXxVOL[6:0] (

“PCM Mixer Channel x Volume” on page 52

)

MSTxMUTE (

“Master Playback Mute” on page 51

)

MSTxVOL[7:0] (

“Master Volume Control” on page 57

)

1

Occur with a soft ramp

Ramp Rate:

1/8 dB every LRCK cycle

FREEZE

Control Port Status

0

Register changes take effect immediately

1

Modifications may be made to all control port registers without the changes taking effect until after the

FREEZE is disabled.

7

6

5

4

3

2

1

0

ADCBMUX1

ADCBMUX0

ADCAMUX1

ADCAMUX0

LINEBMUX

LINEAMUX

HPBMUX

HPAMUX

ADCxMUX[1:0]

Selected Input to ADCx

00

PGAx - Use PGAxMUX bit (

“PGA x Input Select” on page 49

) to select an input channel.

01

AIN1x; PGA is bypassed

10

AIN2x; PGA is bypassed

11

Reserved