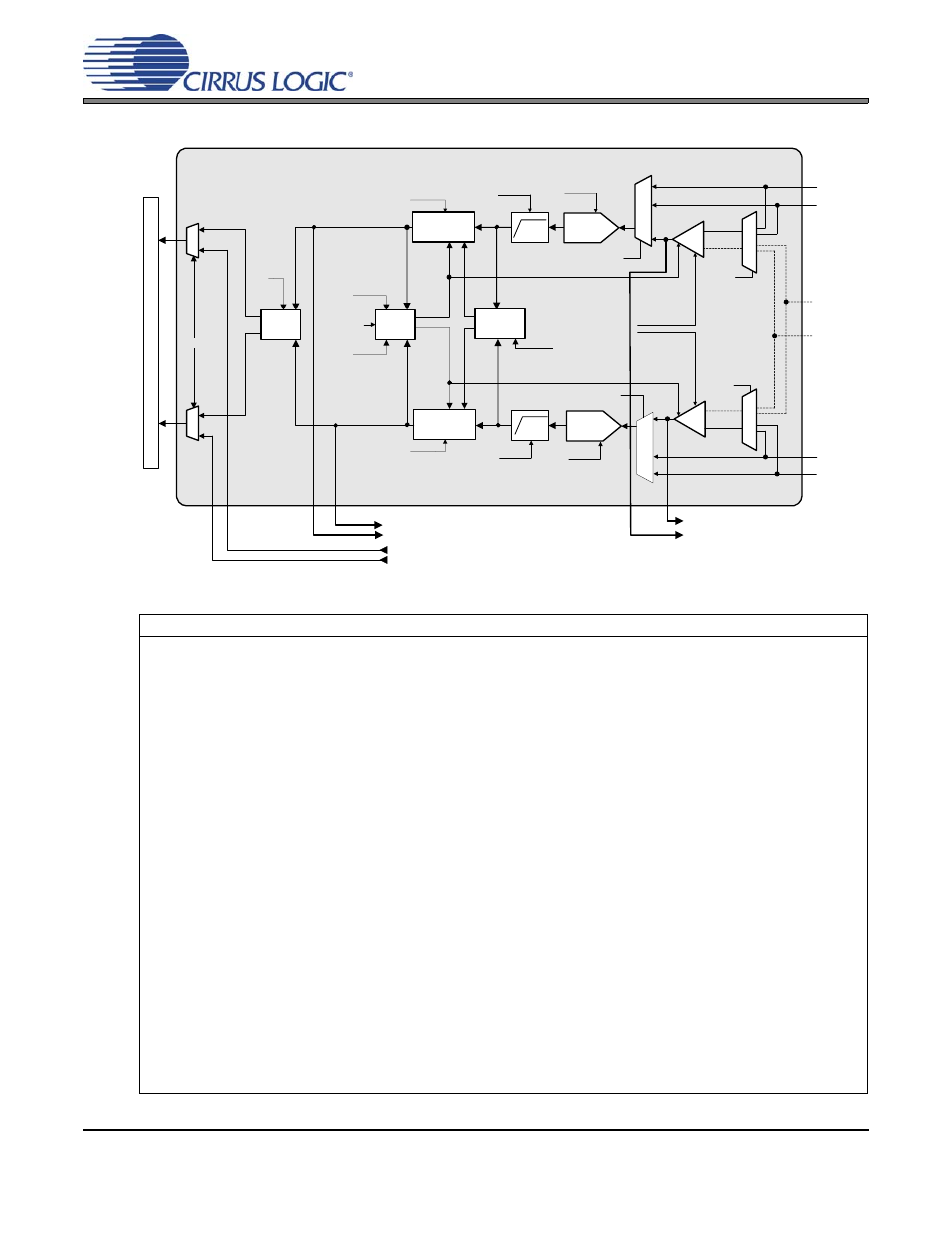

2 analog inputs, Figure 9. analog input signal flow, Figure 9.analog input signal flow – Cirrus Logic CS42L55 User Manual

Page 23: Cs42l55, Referenced control register location

DS773F1

23

CS42L55

4.2

Analog Inputs

Referenced Control

Register Location

Analog Front End

PGAxMUX

PDN_ADCx

PGAxVOL[5:0]

PGAB=A

ANLGZCx

ADCxMUX[1:0]

INV_ADCx

PDN_CHRG

HPFRZx

HPFx

HPFx_CF[1:0]

Digital Volume

BOOSTx

ADCxMUTE

ADCxATT[7:0]

DIGSFT

ADCB=A

ALCx

ALCxSRDIS

ALCxZCDIS

ALCARATE[5:0]

ALCRRATE[5:0]

MAX[2:0]

MIN[2:0]

NGALL

NG

THRESH[3:0]

NGDELAY[1:0]

Miscellaneous

DIGSUM[1:0]

DIGMUX

“PGA x Input Select” on page 49

“Power Down ADC x” on page 42

“PGAx Volume” on page 49

“PGA Channel B=A” on page 48

“Analog Zero Cross” on page 46

“ADC x Input Select” on page 46

“Invert ADC Signal Polarity” on page 48

“Power Down ADC Charge Pump” on page 42

“ADCx High-Pass Filter Freeze” on page 47

“ADCx High-Pass Filter” on page 47

“HPF x Corner Frequency” on page 47

“Boostx” on page 49

“ADC Mute” on page 48

“ADCx Volume” on page 50

“Digital Soft Ramp” on page 46

“ADC Channel B=A” on page 48

“ALCx” on page 62

“ALCx Soft Ramp Disable” on page 65

“ALCx Zero Cross Disable” on page 65

“ALC Attack Rate” on page 63

“ALC Release Rate” on page 63

“ALC Maximum Threshold” on page 64

“ALC Minimum Threshold” on page 64

“Noise Gate All Channels” on page 64

“Noise Gate Enable” on page 65

“Noise Gate Threshold and Boost” on page 65

“Noise Gate Delay Timing” on page 65

“Digital Sum” on page 48

“Digital MUX” on page 45

`

Gain Adjust

ALC

PDN_ADCA

PGAAVOL[5:0]

PGAB=A

ANLGZC

HPFRZA

HPFA

HPFA_CF[1:0]

PDN_ADCA

INV_ADCA

PDN_CHRG

ALCB

ALCBSRDIS

ALCBZCDIS

PC

M Se

ri

a

l

In

te

rf

a

c

e

TO DSP Engine

ALCARATE[5:0]

ALCRRATE[5:0]

MAX[2:0]

MIN[2:0]

ALCA

ALCASRDIS

ALCAZCDIS

AIN1A

AIN2A

ADC

PDN_ADCB

PGABVOL[5:0]

PGAB=A

ANLGZC

BOOSTB

ADCBMUTE

DIGSFT

ADCBATT[7:0]

ADCB=A

HPFRZB

HPB

HPFB_CF[1:0]

PDN_ADCB

INV_ADCB

PDN_CHRG

Noise Gate

NGALL

NG

THRESH[3:0]

NGDELAY[1:0]

Gain Adjust

FROM DSP ENGINE

DIGMUX

AIN1REF

AIN1B

AIN2B

ANALOG PASSTHRU TO

HEADPHONE, LINE AMPLIFIER MUX

Swap/

Mix

DIGSUM[1:0]

BOOSTA

ADCAMUTE

DIGSFT

ADCAATT[7:0]

ADCB=A

ADC

ADCAMUX[1:0]

ADCBMUX[1:0]

AIN2REF

PGAAMUX

PGABMUX

Figure 9. Analog Input Signal Flow