8 cs5341 and miscellaneous control (address 08h), P 22 – Cirrus Logic CDB42438 User Manual

Page 22

CDB42438

22

DS646DB2

5.8

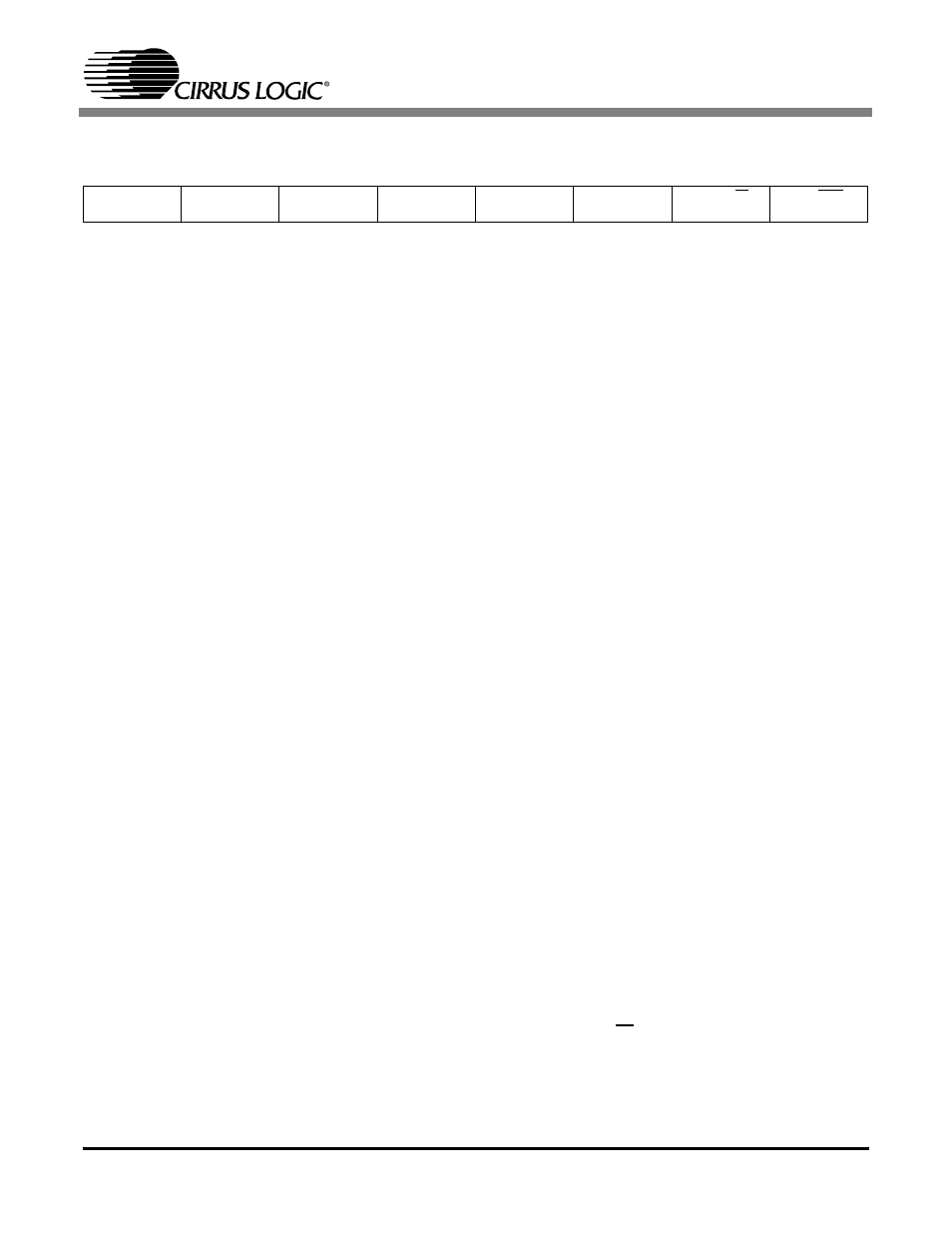

CS5341 AND MISCELLANEOUS CONTROL (ADDRESS 08H)

5.8.1

INT MCLK DIVIDE (1.5/2.0 DIVIDE)

Default = 0

0 - Disabled

1 - Enabled

Function:

Enables/disables the internal (1.5 or 2.0) divide circuitry for MCLK.

5.8.2

1.5 OR 2.0 MCLK DIVIDE (1.5/2.0 DIVIDE)

Default = 0

0 - Divide by 1.5

1 - Divide by 2.0

Function:

Divides the internal MCLK by 1.5 or 2 to all internal logic. This is intended to accommodate an external

MCLK that is greater than 256 Fs. SCLK is derived from MCLK and must always be 256Fs in TDM

Mode (see Figure 6 on page 13).

5.8.3

EXT MCLK DIVIDE (‘41_MCLK_DIV)

Default = 0

0 - Disabled

1 - Enabled

Function:

Enables/disables the internal (1.5 or 2.0) divide circuitry for the CS5341 MCLK.

5.8.4

1.5 OR 2.0 CS5341 MCLK DIVIDE (‘41_DIV_1.5/2.0)

Default = 0

0 - Divide by 1.5

1 - Divide by 2.0

Function:

Divides the MCLK from the MCLK bus to the CS5341 by 1.5 or 2 (see Figure 6 on page 13).

5.8.5

LEFT-JUSTIFIED OR I

²

S INTERFACE FORMAT (‘41_I

²

S/LJ)

Default = 0

0 - Left Justified

1 - I

²

S

7

6

5

4

3

2

1

0

Reserved

Reserved

INT.MCLK_

DIV

INT.DIV_

1.5/2

‘41_MCLK_

DIV

‘41_DIV_

1.5/2

‘41_I²S/LJ

‘41_RST