Appendix b: pll filter, 1 external filter components, 1 general – Cirrus Logic CS42428 User Manual

Page 62: Table 16. pll external component values, 2 capacitor selection, 1 general 9.1.2 capacitor selection

62

DS605F2

CS42428

9. APPENDIX B: PLL FILTER

9.1

External Filter Components

9.1.1

General

The PLL behavior is affected by the external filter component values in the Typical Connection Diagrams.

Figure

and Figure

show the recommended configuration of the two capacitors and one resistor that

comprise the PLL filter. The external PLL component values listed in

have a high corner-frequen-

cy jitter-attenuation curve, take a short time to lock, and offer good output jitter performance. Lock times

are worst case for an Fsi transition of 192 kHz.

It is important to treat the LPFILT pin as a low-level analog input. It is suggested that the ground end of

the PLL filter be returned directly to the AGND pin independently of the digital ground plane.

9.1.2

Capacitor Selection

The type of capacitors used for the PLL filter can have a significant effect on PLL performance. Large or

exotic film capacitors are not necessary because their leads, and the required longer circuit board traces,

add undesirable inductance to the circuit. Surface-mount ceramic capacitors are a good choice because

their own inductance is low, and they can be mounted close to the LPFLT pin to minimize trace induc-

tance. For CRIP, a C0G or NPO dielectric is recommended; and for CFILT, an X7R dielectric is preferred.

Avoid capacitors with large temperature co-coefficient, or capacitors with high dielectric constants, that

are sensitive to shock and vibration. These include the Z5U and Y5V dielectrics.

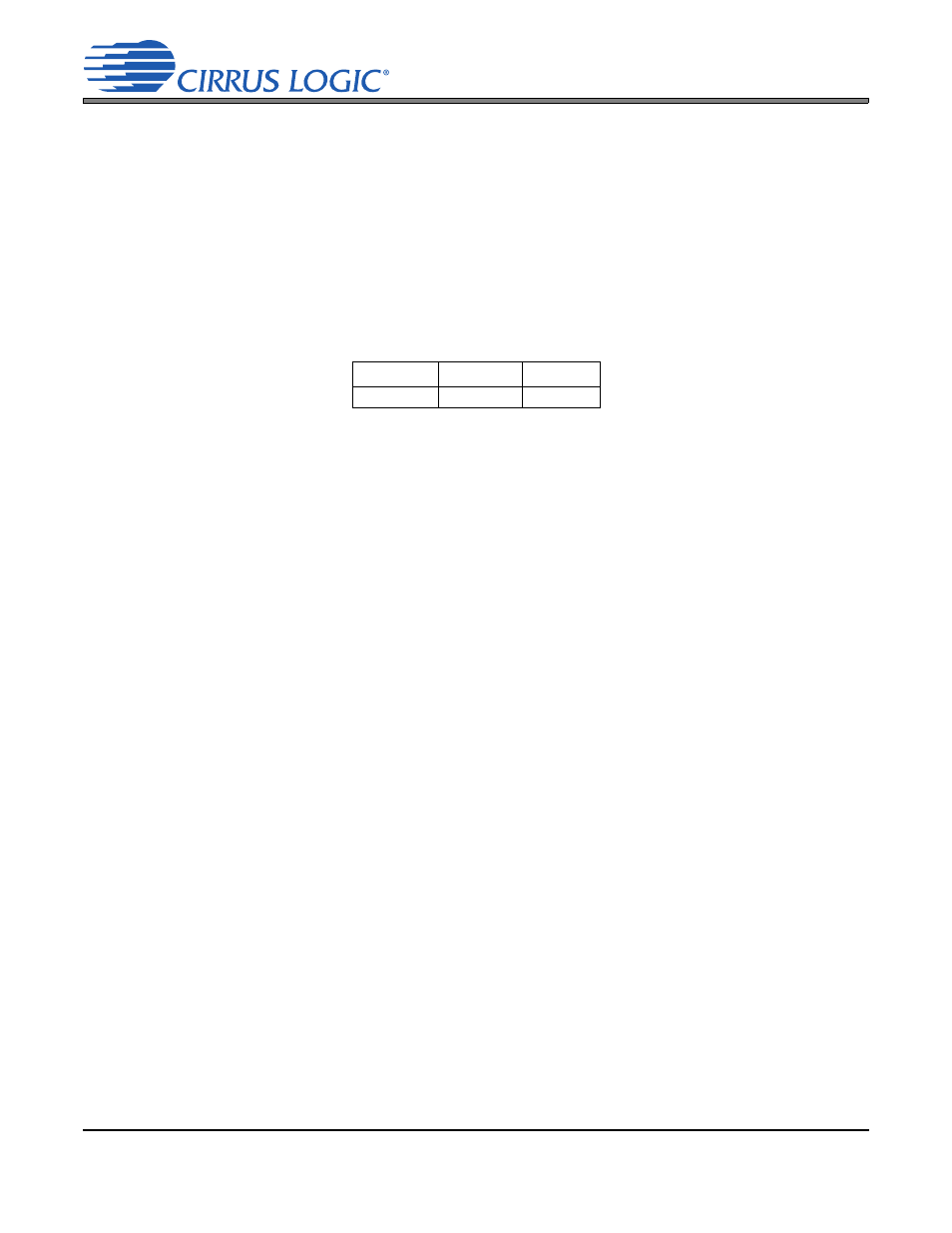

RFILT (k

) CFILT (F) CRIP (pF)

2.55

0.047

2200

Table 16. PLL External Component Values