6 misc control (address 05h), Misc control (address, Misc control (address 05h) – Cirrus Logic CS42428 User Manual

Page 46: Selects

46

DS605F2

CS42428

6.5.4

CODEC RIGHT-JUSTIFIED BITS (CODEC_RJ16)

Default = 0

Function:

This bit determines how many bits to use during Right-Justified Mode for the DAC and ADC. By de-

fault, the DAC and ADC will be in RJ24 bits, but can be set to RJ16 bits.

0 - 24 bit mode.

1 - 16 bit mode.

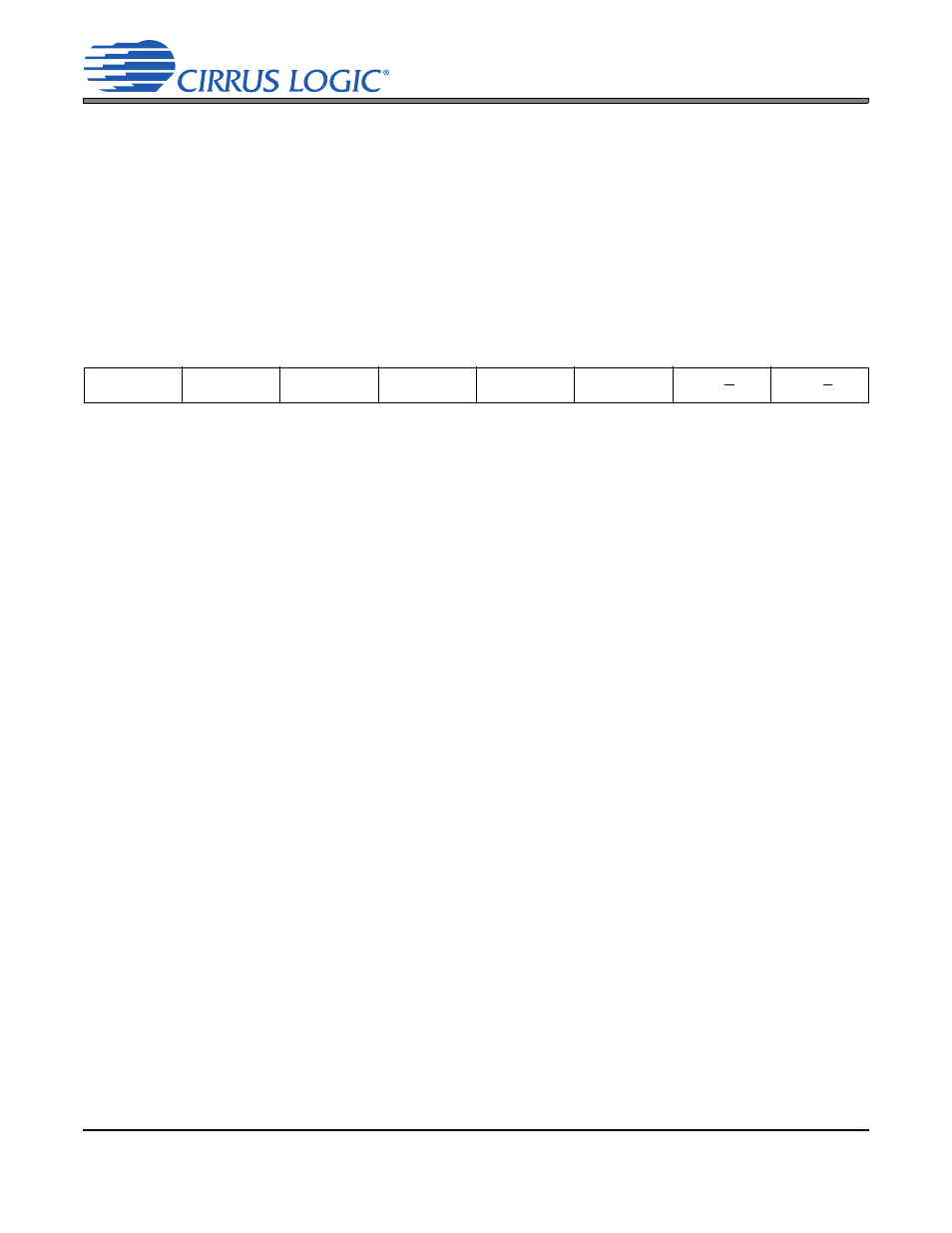

6.6

Misc Control (address 05h)

6.6.1

EXTERNAL ADC SCLK SELECT (EXT ADC SCLK)

Default = 0

Function:

This bit identifies the SCLK source for the external ADCs attached to the ADCIN1/2 ports when using

One-Line Mode of operation.

0 - ADC_SCLK is used as external ADC SCLK.

1 - DAC_SCLK is used as external ADC SCLK.

6.6.2

RMCK HIGH IMPEDANCE (HIZ_RMCK)

Default = 0

Function:

This bit is used to create a high-impedance output on RMCK when the clock signal is not required.

6.6.3

FREEZE CONTROLS (FREEZE)

Default = 0

Function:

This function will freeze the previous output of, and allow modifications to be made to, the Volume

Control (address 0Fh-16h), Channel Invert (address 17h), and Mixing Control Pair (address 18h-1Bh)

registers without the changes taking effect until the FREEZE is disabled. To make multiple changes

in these control port registers take effect simultaneously, enable the FREEZE bit, make all register

changes, then disable the FREEZE bit.

7

6

5

4

3

2

1

0

Ext ADC SCLK

HiZ_RMCK

Reserved

FREEZE

FILT_SEL

HPF_FREEZE

DAC_SP

M/S

ADC_SP

M/S