Table 12. pll clock frequency detection, 9 clock status (address 08h) (read only) – Cirrus Logic CS42428 User Manual

Page 50

50

DS605F2

CS42428

6.9

Clock Status (address 08h) (Read Only)

6.9.1

SYSTEM CLOCK SELECTION (ACTIVE_CLK)

Default = x

0 - Output of PLL

1 - OMCK

Function:

This bit identifies the source of the internal system clock (MCLK).

6.9.2

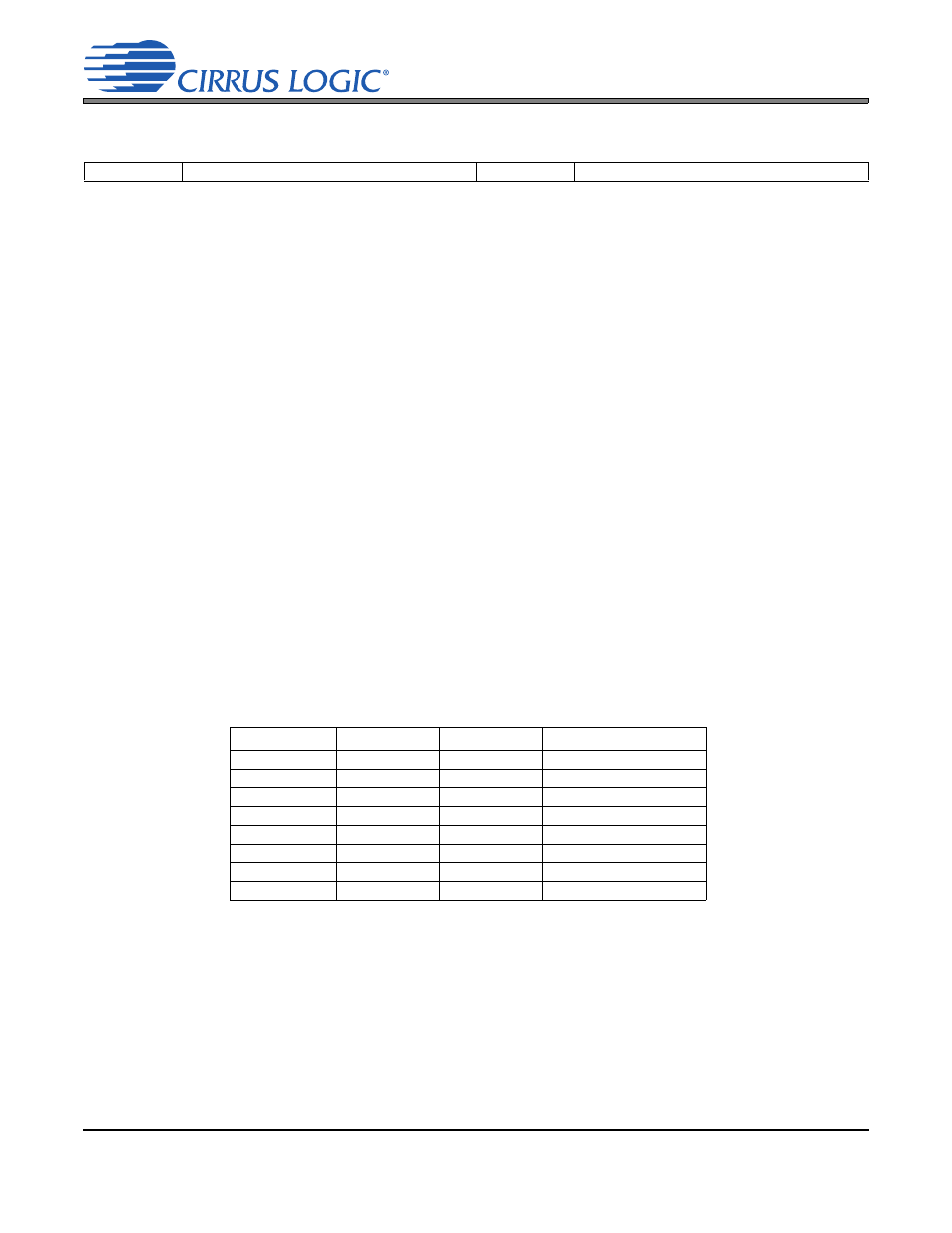

PLL CLOCK FREQUENCY (PLL_CLKX)

Default = xxx

Function:

The CS42428 detects the ratio between the OMCK and the recovered clock from the PLL. Given the

absolute frequency of OMCK, this ratio may be used to determine the absolute frequency of the PLL

clock.

If a 12.2880 MHz, 18.4320 MHz, or 24.5760 MHz clock is applied to OMCK and the OMCK_FREQX

bits are set accordingly (see

“OMCK Frequency (OMCK Freqx)” on page 48

), the absolute frequency

of the PLL clock is reflected in the PLL_CLKX bits according to

. If the absolute frequency of

the PLL clock does not match one of the frequencies given in

, these bits will reflect the clos-

est available value.

If the frequency of OMCK is not equal to 12.2880 MHz, 18.4320 MHz, or 24.5760 MHz, the contents

of the PLL_CLKX bits will be inaccurate and should be disregarded. In this case, an external controller

may use the contents of the OMCK/PLL_CLK ratio register and the known OMCK frequency to de-

termine the absolute frequency of the PLL clock.

Note:

These bits are set to ‘111’b when the FRC_PLL_LK bit is ‘1’b.

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

Active_CLK

PLL_CLK2

PLL_CLK1

PLL_CLK0

PLL_CLK2

PLL_CLK1

PLL_CLK0

Description

0

0

0

8.1920 MHz

0

0

1

11.2896 MHz

0

1

0

12.288 MHz

0

1

1

16.3840 MHz

1

0

0

22.5792 MHz

1

0

1

24.5760 MHz

1

1

0

45.1584 MHz

1

1

1

49.1520 MHz

Table 12. PLL Clock Frequency Detection