2 omck system clock mode, Table 1. common omck clock frequencies, 3 master mode – Cirrus Logic CS42428 User Manual

Page 24: 4 slave mode

24

DS605F2

CS42428

4.4.2

OMCK System Clock Mode

A special clock-switching mode is available that allows the clock that is input through the OMCK pin to be

used as the internal master clock. This feature is controlled by the SW_CTRLx bits in register

trol (address 06h)” on page 48

. An advanced auto-switching mode is also implemented to maintain mas-

ter clock functionality. The clock auto-switching mode allows the clock input through OMCK to be used as

a clock in the system without any disruption when the PLL loses lock, for example, when the LRCK is re-

moved from ADC_LRCK. This clock-switching is done glitch-free. A clock adhering to the specifications

detailed in the Switching Characteristics table on

must be applied to the OMCK pin at all times

that the FRC_PLL_LK bit is set to ‘0’ (See

“Force PLL Lock (FRC_PLL_LK)” on page 49

).

4.4.3

Master Mode

In Master Mode, the serial interface timings are derived from an external clock attached to OMCK or from

the output of the PLL with an input reference to the ADC_LRCK input from the ADC serial port. The DAC

Serial Port and ADC Serial Port can both be masters only when OMCK is used as the clock source. When

using the PLL output, the ADC Serial Port must be slave and the DAC Serial Port can operate in Master

Mode. Master clock selection and operation is configured with the SW_CTRL1:0 bits in the Clock Control

Register (See

“Clock Control (address 06h)” on page 48

).

4.4.4

Slave Mode

In Slave Mode, DAC_LRCK, DAC_SCLK and/or ADC_LRCK and ADC_SCLK operate as inputs. The

Left/Right clock signal must be equal to the sample rate, Fs, and must be synchronously derived from the

supplied master clock, OMCK, or must be synchronous to the supplied ADC_LRCK used as the input to

the PLL. In this latter scenario, the PLL output becomes the internal master clock. The supported PLL out-

put frequencies are shown in

Table 2

.

The serial bit clock, DAC_SCLK and/or ADC_SCLK, must be synchronous to the corresponding DAC_L-

RCK/ADC_LRCK and be equal to 128x, 64x, 48x or 32x Fs, depending on the interface format selected

and desired speed mode.

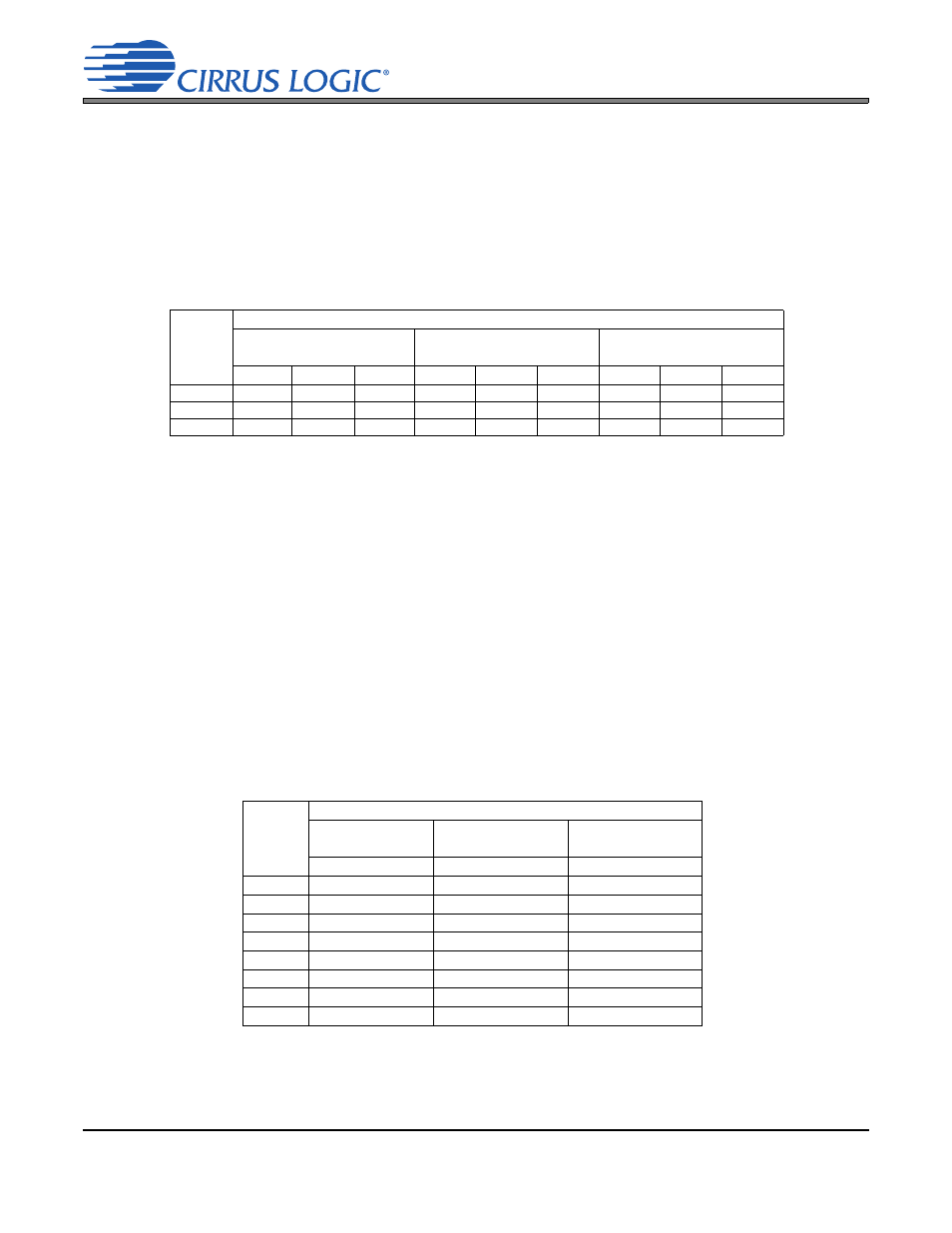

Sample

Rate

(kHz)

OMCK (MHz)

Single-Speed

(4 to 50 kHz)

Double-Speed

(50 to 100 kHz)

Quad-Speed

(100 to 192 kHz)

256x

384x

512x

128x

192x

256x

64x

96x

128x

48

12.2880 18.4320 24.5760

-

-

-

-

-

-

96

-

-

-

12.2880 18.4320 24.5760

-

-

-

192

-

-

-

-

-

-

12.2880 18.4320 24.5760

Table 1. Common OMCK Clock Frequencies

Sample

Rate

(kHz)

PLL Output (MHz)

Single-Speed

(4 to 50kHz)

Double-Speed

(50 to 100kHz)

Quad-Speed

(100 to 192kHz)

256x

256x

256x

32

8.1920

-

-

44.1

11.2896

-

-

48

12.2880

-

-

64

-

16.3840

-

88.2

-

22.5792

-

96

-

24.5760

-

176.4

-

-

45.1584

192

-

-

49.1520