Table 6. digital interface formats, Table 7. adc one-line mode, Table 8. dac one-line mode – Cirrus Logic CS42428 User Manual

Page 45: 5 interface formats (address 04h)

DS605F2

45

CS42428

6.5

Interface Formats (address 04h)

6.5.1

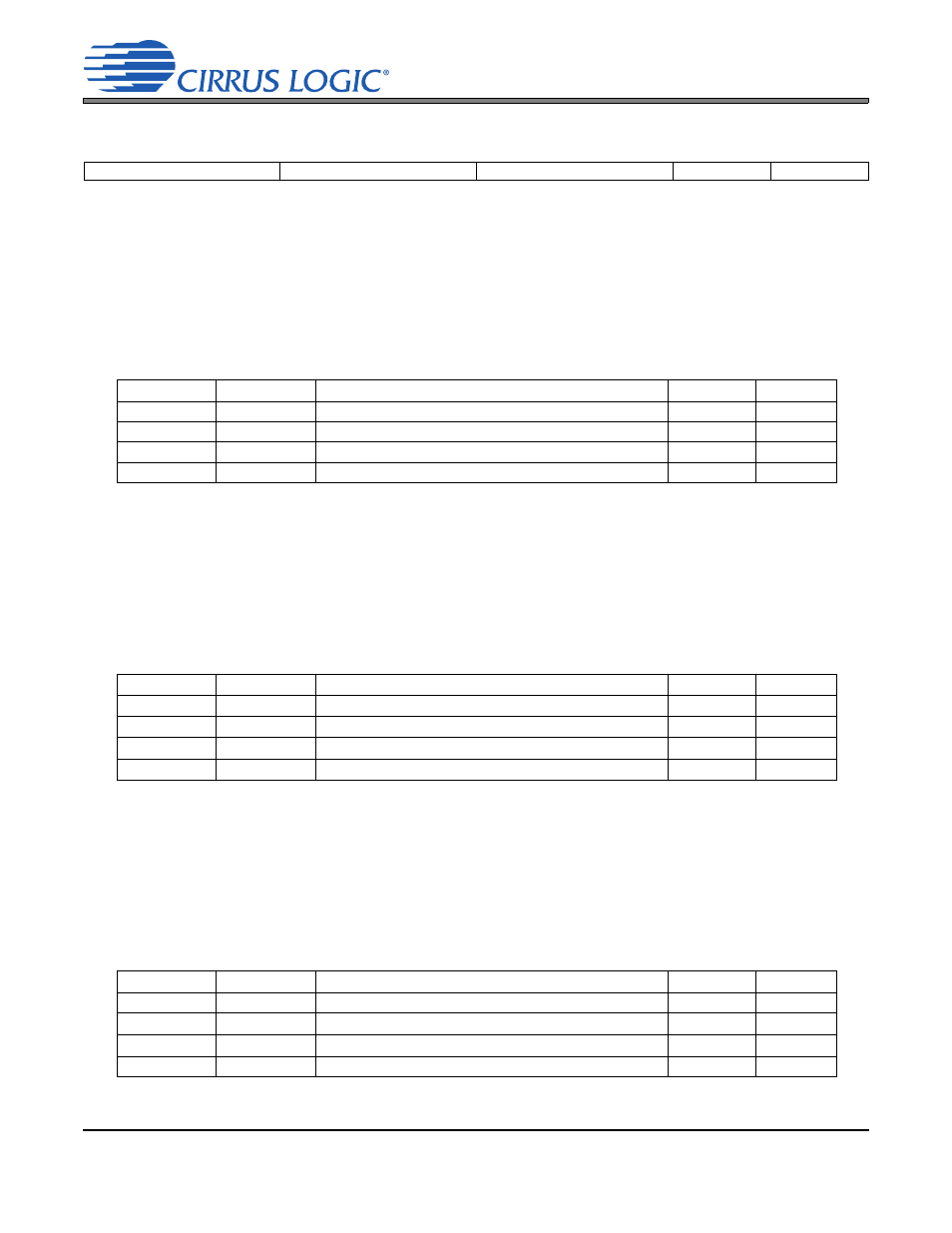

DIGITAL INTERFACE FORMAT (DIFX)

Default = 01

Function:

These bits select the digital interface format used for the ADC & DAC Serial Port when not in One-Line

Mode. The required relationship between the Left/Right clock, serial clock, and serial data is defined by

the Digital Interface Format and the options are detailed in

6.5.2

ADC ONE_LINE MODE (ADC_OLX)

Default = 00

Function:

These bits select which mode the ADC will use. By default, One-Line Mode is disabled, but it can be

selected using these bits. Please see Figures

to see the format of One-Line Mode 1 and

One-Line Mode 2.

6.5.3

DAC ONE_LINE MODE (DAC_OLX)

Default = 00

Function:

These bits select which mode the DAC will use. By default, One-Line Mode is disabled, but it can be

selected using these bits. Please see Figures

to see the format of One-Line Mode 1 and

One-Line Mode 2.

7

6

5

4

3

2

1

0

DIF1

DIF0

ADC_OL1

ADC_OL0

DAC_OL1

DAC_OL0

Reserved

CODEC_RJ16

DIF1

DIF0

Description

Format

Figure

0

0

Left-Justified, up to 24-bit data

0

0

1

I²S, up to 24-bit data

1

1

0

Right-Justified, 16-bit or 24-bit data

2

1

1

Reserved

-

-

Table 6. Digital Interface Formats

ADC_OL1

ADC_OL0

Description

Format

Figure

0

0

DIF: take the DIF setting from reg04h[7:6]

-

-

0

1

One-Line #1

3

1

0

One-Line #2

4

1

1

Reserved

-

-

Table 7. ADC One-Line Mode

DAC_OL1

DAC_OL0

Description

Format

Figure

0

0

DIF: take the DIF setting from reg04h[7:6]

-

-

0

1

One-Line #1

3

1

0

One-Line #2

4

1

1

Reserved

-

-

Table 8. DAC One-Line Mode